Rapid Prototyping Using HDL Coder

Esa-Matti Turtinen and Joonas Järviluoma, Nokia

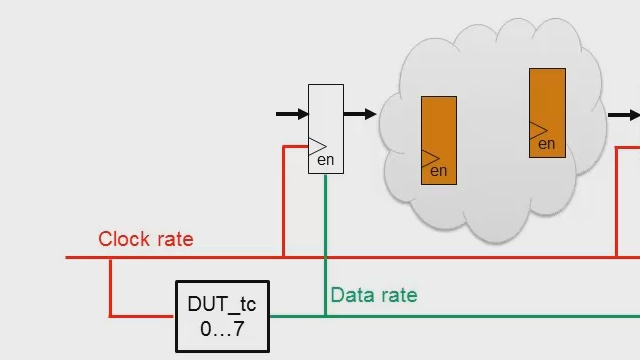

This presentation introduces a high-level synthesis (HLS) workflow for rapid prototyping of wireless communication SoC intellectual property (IP) used at Nokia. The presentation introduces a design and FPGA prototyping workflow of ASICs and presents good design practices targeted for HLS. The presentation also studies HDL code generation with HDL Coder™, possible problems during the workflow, and solutions to overcome those problems. The HLS workflow is examined with an example design that scales and limits the power of IQ-data. This presentation shows the verification of the design in an FPGA environment. It concentrates on evaluating the usage and benefits of HDL Coder HLS workflow targeted for rapid prototyping of SoCs.

Recorded: 21 Apr 2016