HDL Coder Clock Rate Pipelining, Part 2: Optimization

This is part two of a two-part series on clock rate pipelining, using a field-oriented control (FOC) design to illustrate:

- How resource sharing reduces FPGA DSP slice usage at the cost of extra latency

- How clock rate pipelining works with resource sharing to minimize the latency of inserted logic

- How to further optimize the latency of the FOC design

Part one of this series provides an introductory overview on:

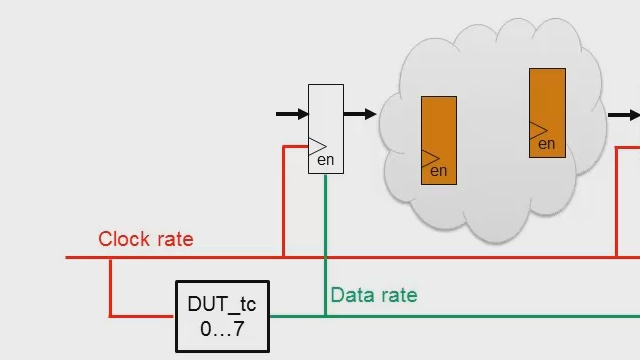

- How Simulink® sample rates map to FPGA clock rates

- How to use HDL Coder™ oversampling together with clock rate pipelining to control optimization

Published: 25 May 2016