What Is HDL Coder?

HDL Coder™ enables high-level design for FPGAs, SoCs, and ASICs by generating synthesizable Verilog® and VHDL® code from MATLAB® functions, Simulink® models, and Stateflow® charts. You can use the generated HDL code for FPGA programming, ASIC prototyping, and production design.

HDL Coder includes a workflow advisor that automates prototyping generated code on Xilinx®, Intel®, and Microchip boards and generates IP cores for ASIC and FPGA workflows. You can optimize for speed and area, highlight critical paths, and generate resource utilization estimates before synthesis. HDL Coder provides traceability between Simulink models and generated Verilog and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

HDL Coder generates synthesizable Verilog and VHDL code from your MATLAB functions, Simulink models, Stateflow charts, and Simscape models

You can design high-level algorithms in MATLAB and Simulink, prototype on FPGAs, and implement on production FPGAs and ASICs.

You can generate HDL code from more than 200 MATLAB functions, 300 Simulink blocks, Stateflow charts,

and Simulink models for domain-specific applications.

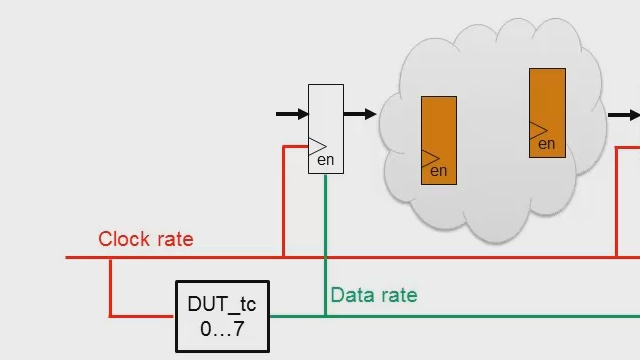

You can enable a combination of speed, area, and I/O optimizations, such as pipelining, resource sharing, and frame-to-sample conversion, to generate multiple architectures without making changes to the MATLAB function or Simulink model

Explore the design space by analyzing speed and area tradeoffs to meet design constraints and identify the desired solution.

HDL Coder supports floating-point implementation and floating-point-to-fixed-point conversion. You can mix them in your design based on dynamic range requirements.

Integration with FPGA vendor tools enables you to automate the development process all the way through FPGA board programming. You can also generate IP cores that can be integrated into larger designs using FPGA or ASIC workflows.

Support for high-level synthesis tools like Cadence Stratus makes it easy for you to create highly-optimized ASIC implementations with insights into timing, area, and power.

Code generation reports help you evaluate expected usage of hardware resources, identify critical paths, and measure latency.

The generated HDL code is well-structured, commented, and readable.

For greater traceability, you can navigate from HDL code to its source, or navigate from the model to its corresponding code.

HDL Coder supports development of systems adhering to functional safety standards like DO-254.

For more information, please visit the HDL Coder product page.