## Rapid Prototyping Using HDL Coder

#### Who Are We?

Esa-Matti Turtinen

Joonas Järviluoma

R&D Manager, SoC Prototyping, Nokia Oulu Prototype Engineer, SoC, Nokia Oulu

- M.Sc., Electrical Engineering

- 31 years old

- About 6 years of experience working on different roles related to SoC development

- M.Sc., Electrical Engineering

- 26 years old

- Just graduated

- Currently working on FPGA lab testing

# Expanding the human possibilities of the connected world

## Nokia has been at the forefront of every fundamental change in how we communicate and connect

| Telephony<br>begins | Analog<br>revolution<br>Long distance voice<br>communication | Digital<br>revolution<br>Voice, data, and video<br>communication | Mobile<br>revolution<br>Wireless<br>communication | The new<br>connectivity<br>Intelligent and seamless<br>connectivity through the Cloud |

|---------------------|--------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------|

|                     |                                                              |                                                                  |                                                   |                                                                                       |

Internet of Things

νισκιδ

4 © Nokia 2016

#### A financially strong leader

#### R&D professionals

#### Services professionals

World leading intellectual property (patent families)

#### Bell Labs

Nokia Technologies

### ~40,000

~40,000

~31,000

#### 6 © Nokia 2016

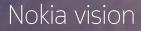

Challenge

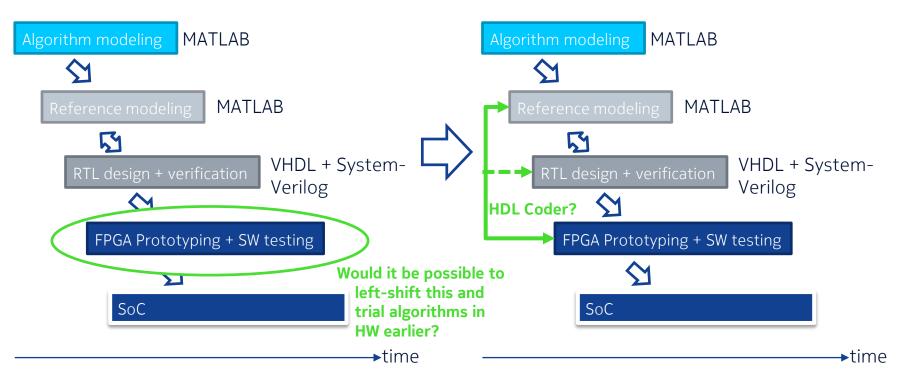

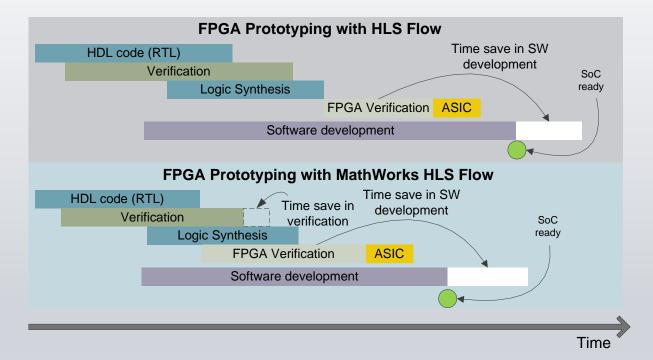

#### FPGA Prototyping Flow Timeline Proportional Estimation in Generic HLS flow

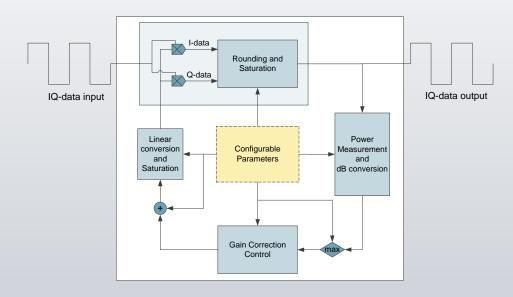

#### Example Design for HDL Coder Flow Scaling and Power Limitation Block

- Arithmetic logic (multipliers, adders etc.)

- Loop structures

- State-Machine

- Look-up tables for dB conversions

- Registers for state control and buffering

- Variable indexing

- Configurable parameters

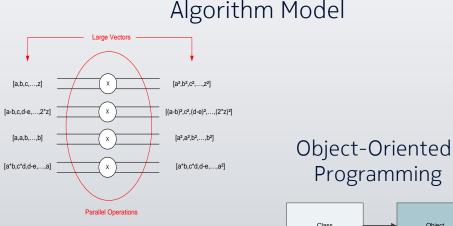

#### Classic Division of Models Algorithm and RTL

MATLAB operations optimized for maximized simulation performance

#### RTL Model

- Hand-written based on algorithm model

- ASIC optimized performance

- Thorough verification required

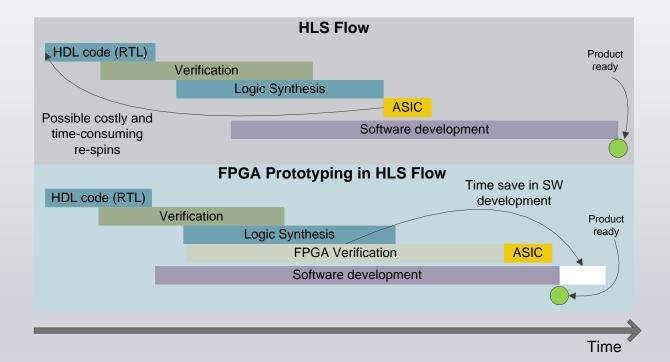

#### Division in HDL Coder Workflow Algorithm and RTL

Algorithm Model:

- Written in MATLAB function blocks/System Objects and Simulink library components

- Has to be written from HW perspective to generate feasible RTL

#### RTL Model:

- Rapid generation from Simulink (or MATLAB) model

- Verification focus moves towards algorithm

- Cosimulation verificates RTL against algorithm model

- "Is as good as the algorithm"

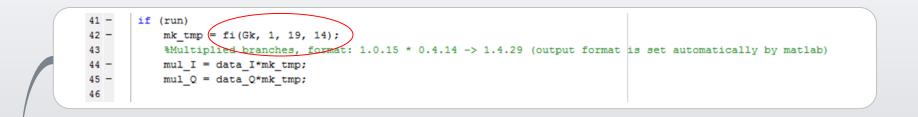

#### RTL Generation Example 1: Algorithm without Data Type Definition

```

if (run)

mk_tmp = Gk;

%Multiplied branches, format: 1.0.15 * 0.4.14 -> 1.4.29 (output format is set automatically by matlab)

mul_I = data_I*mk_tmp;

mul_Q = data_Q*mk_tmp;

```

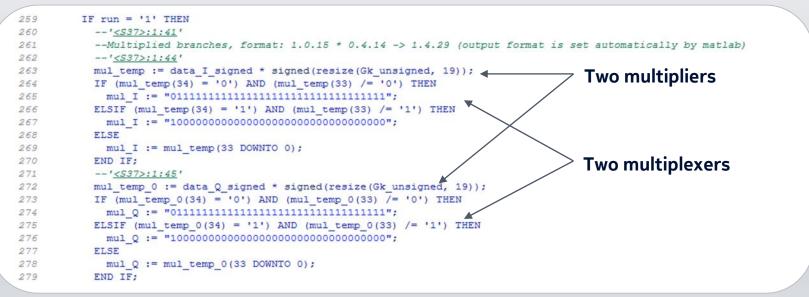

#### RTL Generation Example 2: Algorithm with Data Type Definition

| 258 | IF run = '1' THEN                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------|

| 259 | ' <u>&lt;\$37&gt;:1:41</u> '                                                                          |

| 260 | ' <u>&lt;\$37&gt;:1:42</u> '                                                                          |

| 261 | <pre>mk tmp := signed(resize(Gk unsigned, 19));</pre>                                                 |

| 262 | Multiplied branches, format: 1.0.15 * 0.4.14 -> 1.4.29 (output format is set automatically by matlab) |

| 263 | ' <u>&lt;\$37&gt;:1:44</u> '                                                                          |

| 264 | <pre>mul I := data I signed * mk tmp;</pre>                                                           |

| 265 | ' <u><s37>:1:45</s37></u> ' Two multipliers                                                           |

| 266 | <pre>mul_Q := data_Q_signed * mk_tmp;</pre>                                                           |

|     |                                                                                                       |

#### NOKIA

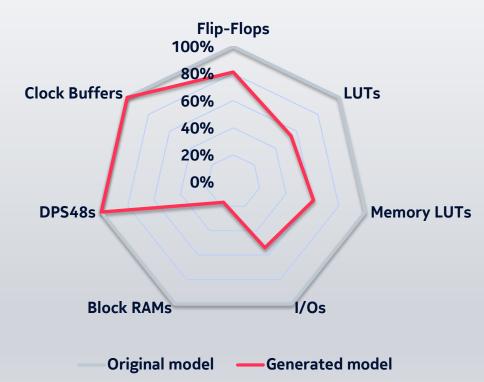

#### RTL Resource Utilization Comparison FPGA Prototype Vs. Original ASIC Targeted Model

- Original hand-written model, targeted for ASIC, had slightly more signals and routing logic compared to generated model!

- Generated model tested succesfully in FPGA-inthe-loop configuration

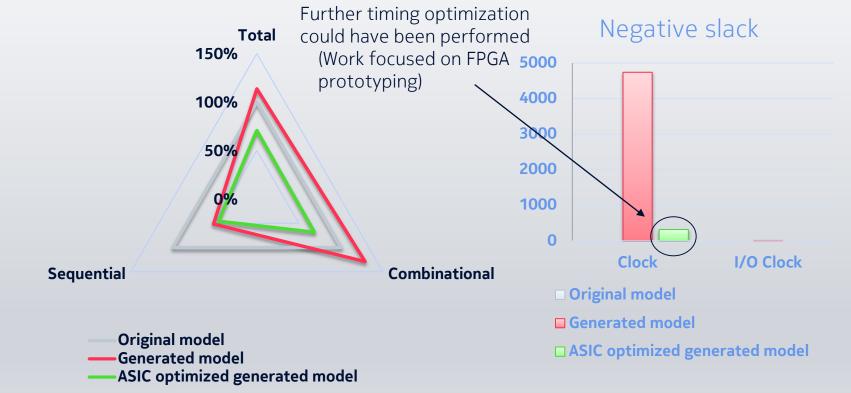

#### ASIC Optimization Area and Timing Results

#### NOKIA

#### FPGA Prototyping Flow Timeline Proportional Estimation in HDL Coder Flow

#### Conclusion Benefits and Shortages

#### Benefits:

- Human readable HDL output

- Design work and verification focus moves on higher level

- Good synthesis results in both FPGA and ASIC cases

- Distinct GUI

- Support for 3rd party tools and FPGA boards

#### Shortages:

- For feasible HDL generation and FPGA prototyping, algorithms have to be written strictly from HW perspective

- No trivial way to generate generic variables to create scalable lps (due to Model-Based Design flow)

#### Future Work

Algorithm design work change towards RTL design style required

- Close co-operation with algorithm and RTL designers is vital

- Algorithm simulation speed might be critical

IP generation with generic interfaces

- Was left out of scope in this study

- Needs to be verified

Projects ongoing