Pixel Stream Aligner

Align two streams of pixel data

Libraries:

Vision HDL Toolbox /

Utilities

Description

The Pixel Stream Aligner block synchronizes two pixel streams by delaying one stream to match the timing of a reference stream. Many Vision HDL Toolbox™ algorithms delay the pixel stream, and the amount of delay can change as you adjust algorithm parameters. You can use this block to align streams for overlaying, comparing, or combining two streams such as in a Gaussian blur operation. Connect the delayed stream to the refPixel and refCtrl input ports, and the earlier stream to the pixel and ctrl input ports.

This waveform diagram shows the input streams, pixelIn and

refPixelIn, and their associated control signals. The reference

input frame starts later than the pixelIn frame. The output signals

show that the block delays pixelIn to match the reference stream, and

that both output streams share control signals. The waveform shows the short latency

between the input refCtrl and the output refCtrl.

In this simulation, to accommodate the delay of four lines between the input streams,

the Maximum number of lines parameter must be set to at least

4.

Examples

Harris Corner Detection

Use edge detection as the first step in corner detection. The algorithm is suitable for FPGAs.

Ports

Input

This block uses a streaming pixel interface with a bus for

frame control signals. This interface enables the block to operate independently of image size

and format. The pixel ports on this block support single pixel streaming or

multipixel streaming. Single pixel streaming accepts and returns a single pixel value each clock

cycle. Multipixel streaming accepts and returns a vector of M pixels per

clock cycle to support high-frame-rate or high-resolution formats. The M

value corresponds to the Number of pixels parameter of the Frame

To Pixels block. Along with the pixel, the block accepts and returns a

pixelcontrol bus that contains five control signals. The control signals

indicate the validity of each pixel and their location in the frame. For multipixel streaming,

one set of control signals applies to all pixels in the vector. To convert a frame (pixel

matrix) into a serial pixel stream and control signals, use the Frame

To Pixels block. For a full description of the interface, see Streaming Pixel Interface.

This block also supports multipixel-multicomponent streams, where the pixel input is a matrix of M-by-N values. M is number of pixels and N is number of components. These values correspond to the Number of pixels and Number of components parameters of the Frame To Pixels block.

For single pixel streams, specify pixel as a scalar or a vector of 1-by-Number of components values. For multipixel streams, specify pixel as a matrix of Number of pixels-by-Number of components pixel intensity values. Number of pixels can be two, four, or eight.

Because the block delays this pixel stream to match the control signals of the reference stream, refPixel, pixel must be the earlier of the two streams.

Since R2025a, the software supports single

data type for simulation and HDL code generation. To enable HDL code generation for

single data types in your model, open the HDL

Coder app, go to the Floating Point pane, and

select the Use Floating Point checkbox.

double data type is supported only for simulation, not for HDL code

generation.

Data Types: fixed point | uint | int | Boolean | double | single

The pixelcontrol bus contains five signals.

The signals describe the validity of the pixel and its location in the frame. For more

information, see Pixel Control Bus.

For multipixel streaming, each vector of pixel values has one set of control signals.

Because the vector has only one valid signal, the pixels in the

vector must be either all valid or all invalid. The hStart and

vStart signals apply to the pixel with the lowest index in the

vector. The hEnd and vEnd signals apply to the

pixel with the highest index in the vector.

Data Types: bus

Specify refPixel as a scalar, a vector of 1-by-Number of components values, or a matrix of Number of pixels-by-Number of components pixel intensity values.

The allowed dimensions for refPixel depend on the dimensions of the input pixel stream. The Number of pixels must be the same.

| Input pixel Dimensions | Allowed refPixel Dimensions |

|---|---|

| 1-by-N | 1-by-1, 1-by-3, or 1-by-4 |

| 2-by-N | 2-by-1, 2-by-3, or 2-by-4 |

| 4-by-N | 4-by-1, 4-by-3, or 4-by-4 |

| 8-by-N | 8-by-1, 8-by-3, or 8-by-4 |

Because the block delays the pixel input stream to match the reference control signals, refPixel must be the later of the two streams. The reference data and its control signals pass through the block with a small delay.

Since R2025a, the software supports single

data type for simulation and HDL code generation. To enable HDL code generation for

single data types in your model, open the HDL

Coder app, go to the Floating Point pane, and

select the Use Floating Point checkbox.

double data type is supported only for simulation, not for HDL code

generation.

Data Types: fixed point | uint | int | Boolean | double | single

The pixelcontrol bus contains five signals.

The signals describe the validity of the pixel and its location in the frame. For more

information, see Pixel Control Bus.

For multipixel streaming, each vector of pixel values has one set of

control signals. Because the vector has only one

valid signal, the pixels in the vector must be

either all valid or all invalid. The hStart and

vStart signals apply to the pixel with the lowest

index in the vector. The hEnd and

vEnd signals apply to the pixel with the highest

index in the vector.

The block uses these control signals for the aligned output stream.

Data Types: bus

Output

The timing of the output pixel stream matches the timing of the output refPixel stream. The dimensions and data type of the output pixel stream match those of the input pixel stream.

Data Types: fixed point | uint | int | Boolean | double | single

The dimensions and data type of the output refPixel stream match those of the input refPixel stream. The block passes this stream through the block unchanged.

Data Types: fixed point | uint | int | Boolean | double | single

The block passes the input refCtrl signals through the block with a small delay.

Data Types: bus

Parameters

Choose a power of two that accommodates the number of active pixels in a horizontal line. If you specify a value that is not a power of two, the block uses the next largest power of two. The block implements a circular buffer of 2m pixels, where m is log2(Maximum number of lines) + log2(Line buffer size).

When you use multipixel input, this value must accommodate (Active pixels per line)/(Number of pixels) + 2.

The block implements a circular buffer of 2m pixels, where m is log2(Maximum number of lines) + log2(Line buffer size), and a line address buffer of Maximum number of lines locations. The circular memory stores the earlier input lines until the reference control signals arrive. The line address buffer stores the address of the start of each line. When the reference control signals arrive, the block uses the stored address to read and send the delayed line. This parameter must accommodate the difference in timing between the two input streams, including the internal latency before the block reads the first line. During simulation, the block warns when an overflow occurs. To avoid the overflow condition, increase Maximum number of lines. The delay between streams cannot exceed an entire frame.

When the input pixel is a vector or a matrix, the block replicates the circular buffer for each element. For multipixel streaming, the block adjusts the line buffer size to store 1/Number of pixels pixels. For instance, with a 4-by-3 input stream, each buffer stores ¼ of the pixels for a line, and the buffer is 12×2m-2 locations. The line address buffer remains the same size.

Algorithms

The block stores the data from the pixel input port to a circular buffer and then reads the lines out to align with the reference control signals. The block also stores the address of the start of each line. To match the added processing delay of the buffer data path, the block delays the reference pixel data and control signals for around 10 cycles.

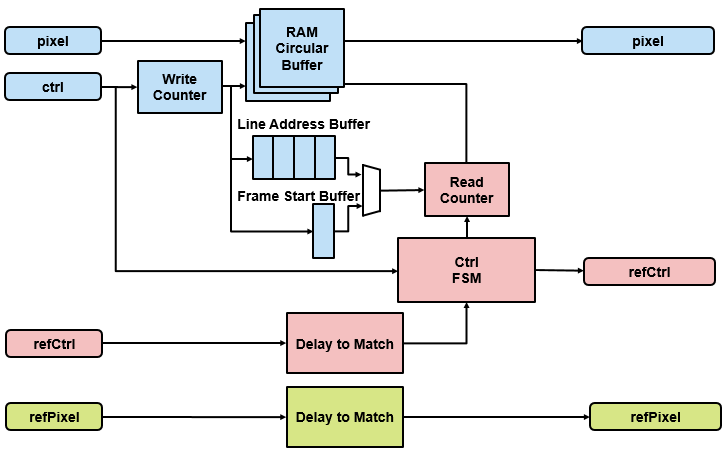

The diagram shows the architecture of the block. The RAM Circular Buffer is a memory of

2m pixels, where

m is log2(Maximum number of

lines) + log2(Line buffer

size). The Line Address Buffer has Maximum number of

lines locations. If the number of ctrl.Hstart

assertions before the first refCtrl.Hstart assertion is greater than

the size of the Line Address Buffer, the block overwrites both buffers and corrupts the

output. In this diagram, Maximum number of lines is four, so four

locations exist to store a line address in the buffer. The Frame Start Buffer is a

single location to store ctrl.Vstart. The delay between the two

streams must be less than the time between frame starts.

When the input pixel is a vector or a matrix, the block replicates the RAM Circular Buffer for each element. The diagram shows three RAM Circular Buffers, to represent a three-component pixel stream. Each RAM Circular Buffer is 2m memory locations. For multipixel streaming, the block adjusts the line buffer size to store 1/Number of pixels pixels. For instance, with a 4-by-3 input stream, each buffer stores ¼ of the pixels for a line, and there are 12 RAM Circular Buffers, each with 2m-2 locations. The line address buffer remains the same size.

This table shows the resource use after synthesis of the block for the Xilinx®

Zynq®-7000 SoC ZC706 Evaluation Kit with single-pixel

uint8 input and the default parameter settings. The design

achieves a clock frequency of 306 MHz.

| Resource | Usage |

|---|---|

| Slice LUTs | 265 |

| Slice Registers | 492 |

| DSP48 | 0 |

| Block RAM | 48 |

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2017aThe block now supports HDL code generation with single data

type pixel input.

The block now supports multipixel streams that have 2 pixels per clock cycle.

The block now supports streams that are both multipixel and multicomponent. The HDL implementation replicates the algorithm for each pixel and component in parallel.

The block supports input and output matrices of

NumPixels-by-NumComponents pixels, where

NumPixels is 4 or 8. The ctrl ports

remain scalar, and the control signals in the pixelcontrol bus

apply to all pixels in the matrix.

The Pixel Stream Aligner block now supports multipixel streams. The HDL implementation replicates the algorithm for each pixel in parallel. You cannot use multicomponent and multipixel together.

For multipixel streaming, the block supports input and output column vectors of 4

or 8 pixels. The ctrl port remains scalar, and the control

signals in the pixelcontrol bus apply to all pixels in the

vector.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)