Multiprocessor Execution

SoC Blockset™ enables simulation of multiprocessor executions as they behave on a multiprocessor SoC. In multiprocessor simulations, each processor reference model executes simultaneously, where each processor execution is managed by an independent Task Manager block representing either the OS or bare-metal scheduler for that processor. Processors can interact with each other using interprocessor communication channels, through the Interprocess Data Channel block, enabling for synchronization of tasks and algorithms between the task manager of each processor.

Multiprocessor SoC Model

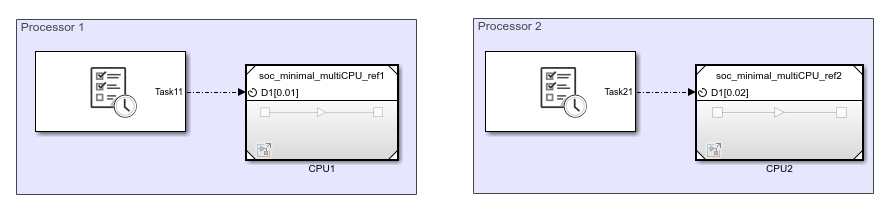

A multiprocessor SoC model contains at least two Task Manager blocks, each connected to a Model block representing the process to be run on a separate processor. This figure shows a minimal independent two-processor system.

In simulation, each Task Manager and Model block automatically acts as an independent processor. The tasks assigned to different Task Manager blocks run independently of the other processor while tasks within a single Task Manager block still behave dependently. For more information of task execution within a single processor, see What is Task Execution? and Multicore Execution and Core Visualization.

Note

All tasks within the top-level model must use a unique identifier name.

Processors can communicate to each other asynchronously using a interprocess data channel. An interprocess data channel consists of the Interprocess Data Write, Interprocess Data Channel, and Interprocess Data Read blocks. For more information on processor to processor communication channels, see Interprocess Data Communication via Dedicated Hardware Peripheral.

In code generation, the top-level Simulink® model and each reference model must have their Hardware board parameter set to

a supported multiprocessor hardware board. In the top-level model, you must

set the Processing Unit parameter to none to

indicate that the model does not build. In each reference model, you must set the

Processing Unit parameter to a specific processor.

See Also

Task Manager | Interprocess Data Write | Interprocess Data Channel | Interprocess Data Read