Complex to Magnitude-Angle

Compute magnitude and phase angle of complex signal using CORDIC algorithm

Libraries:

DSP HDL Toolbox /

Math Functions

Description

The Complex to Magnitude-Angle block computes the magnitude and phase angle of a complex signal and provides hardware-friendly control signals. To achieve an efficient HDL implementation, the block uses a pipelined Coordinate Rotation Digital Computer (CORDIC) algorithm.

You can use this block to implement operations such as atan2 in hardware.

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a Simulink® model, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the Simulink block.

Examples

Implement atan2 Function for HDL

Implement the atan2 function in hardware by using the

Complex to Magnitude Angle block.

Ports

Input

Complex input signal, specified as a scalar, a column vector representing samples in time, or a row vector representing channels. Using vector input increases data throughput while using more hardware resources. The block implements the conversion logic in parallel for each element of the vector. The input vector can contain up to 64 elements.

The software supports double and

single data types for simulation, but not for HDL code generation.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Complex Number Support: Yes

Control signal that indicates if the input data is valid. When

valid is 1 (true), the

block captures values from the input data port. When

valid is 0 (false), the

block ignores the values from the input data port.

Data Types: Boolean

Output

Magnitude of the input signal, returned as a scalar, a column vector representing samples in time, or a row vector representing channels. The dimensions of this port match the dimensions of the input data port.

Dependencies

To enable this port, set the Output format parameter to

Magnitude and Angle or Magnitude.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

Angle of the input signal, returned as a scalar, a column vector representing samples in time, or a row vector representing channels. The dimensions of this port match the dimensions of the input data port.

Dependencies

To enable this port, set the Output format parameter to

Magnitude and Angle or Angle.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

Control signal that indicates if the data from the output

data port is valid. When valid is

1 (true), the block returns valid data from

the Magnitude and/or Angle ports. When

valid is 0 (false), the

values from the Magnitude and/or Angle ports

are not valid.

Data Types: Boolean

Parameters

Note

These parameters apply when configuring a block in Simulink or an algorithm in the DSP HDL IP Designer app.

To set the number of iterations to input WL − 1, select

Auto. If the input is of data typedoubleorsingle, the number of iterations is set to 16, by default.To specify the number of iterations by using Number of iterations parameter, select

Property.

The number of iterations must be less than or equal to input WL − 1. The latency of the block depends on the number of iterations performed. For information about latency, see Latency.

Dependencies

To enable this parameter, set Number of iterations source to

Property.

Use this parameter to specify which output ports are enabled.

To enable the Magnitude and Angle output ports, select

Magnitude and Angle(default).To enable the Magnitude output port and disable the Angle output port, select

Magnitude.To enable the Angle output port and disable the Magnitude output port, select

Angle.

To return the Angle output as a fixed-point value that normalizes the angles in the range [–1,1], select

Normalized. For more information see Normalized Angle Format.To return the Angle output as a fixed-point value in the range [-π, π], select

Radians. When using this block to implement theatan2function, set this parameter toRadians.

Select this parameter to multiply the Magnitude output by the inverse of the CORDIC gain factor. The block implements this gain factor with either CSD logic or a multiplier, according to the Scaling method parameter.

Note

If you clear this parameter and apply the CORDIC gain elsewhere in your design,

you must exclude the π/4 term. Because the quadrant mapping algorithm replaces the

first CORDIC iteration by mapping inputs onto the angle range [0, π/4], the initial

rotation does not contribute a gain term. The gain factor is the product of

cos(atan(2-n)), for

n from 1 to Number of iterations – 1.

Dependencies

To enable this parameter, set the Output format parameter to

Magnitude and Angle or Magnitude.

When you set this parameter to Shift-Add, the block

implements the CORDIC gain scaling by using a shift-and-add architecture for the

multiply operation. This implementation uses no multiplier resources and may increase

the length of the critical path in your design. When you select

Multipliers, the block implements the CORDIC gain scaling

with a multiplier and increases the latency of the block by four

cycles.

Dependencies

To enable this parameter, select the Scale output parameter.

Algorithms

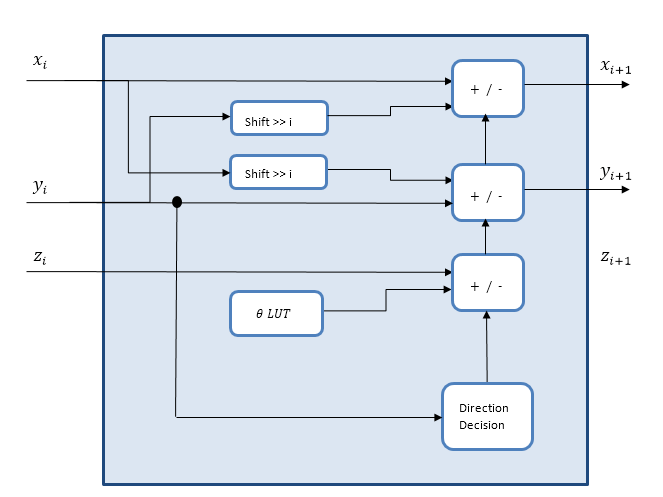

The CORDIC algorithm is a hardware-friendly method for performing trigonometric functions. It is an iterative algorithm that approximates the solution by converging toward the ideal point. The block uses CORDIC vectoring mode to iteratively rotate the input onto the real axis.

Givens method for rotating a complex number x+iy by an angle θ is as follows. The direction of rotation, d, is +1 for counterclockwise and −1 for clockwise.

For a hardware implementation, factor out the cosθ to leave a tanθ term.

To rotate the vector onto the real axis, choose a series of rotations of θn so that . Remove the cosθ term so each iterative rotation uses only shift and add operations.

Combine the missing cosθ terms from each iteration into a constant, and apply it with a single multiplier to the result of the final rotation. The output magnitude is the scaled final value of x. The output angle, z, is the sum of the rotation angles.

The convergence region for the standard CORDIC rotation is ≈±99.7°. To work around this limitation, before doing any rotation, the block maps the input into the [0, π/4] range using this algorithm.

if abs(x) > abs(y) input_mapped = [abs(x), abs(y)]; else input_mapped = [abs(y), abs(x)]; end

Quadrant mapping saves hardware resources and reduces latency by reducing the number of CORDIC pipeline stages by one. The CORDIC gain factor, Kn, therefore does not include the n=0, or cos(π/4)term.

After the CORDIC iterations are complete, the block adjusts the angle back to its original location. First it adjusts the angle to the correct side of π/4.

if abs(x) > abs(y) angle_unmapped = CORDIC_out; else angle_unmapped = (pi/2) - CORDIC_out; end

if (x < 0)

if (y < 0)

output_angle = - pi + angle_unmapped;

else

output_angle = pi - angle_unmapped;

else

if (y<0)

output_angle = -angle_unmapped;

The block generates a pipelined HDL architecture to maximize throughput. Each CORDIC

iteration is done in one pipeline stage. The gain factor, if enabled, is implemented with

canonical signed digit (CSD) logic by default. Set the Scaling method

parameter to Multipliers to implement the gain factor with a

multiplier.

If you use vector input, this block replicates this architecture in parallel for each element of the vector.

The following table shows Magnitude and Angle output word length (WL), for particular input word length (WL). FL stands for fractional length used in fixed-point representation.

| Input Word Length | Output Magnitude Word Length |

|---|---|

| fixdt(0,WL,FL) | fixdt(0,WL + 2,FL) |

| fixdt(1,WL,FL) | fixdt(1,WL + 1,FL) |

| Input Word Length | Output Angle Word Length | |

|---|---|---|

| fixdt([ ],WL,FL) | Radians | fixdt(1,WL + 3,WL) |

| Normalized | fixdt(1,WL + 3,WL+2) | |

The CORDIC logic at each pipeline stage implements one iteration. For each pipeline stage, the shift and angle rotation are constants.

When you set Output format to Magnitude,

the block does not generate HDL code for the angle accumulation and quadrant correction

logic.

This format normalizes the fixed-point radian angle values around the unit circle. This use of bits can be more efficient than the use of the range [0, 2π] radians. Also this normalized angle format enables wraparound of angle at 0 or 2π without additional detect and correct logic.

For example, representing the angle with 3 bits results in these normalized values.

The block normalizes the angles across [0, π/4] and maps them to the correct octant at the end of the calculation.

When the valid input is applied, the block returns valid output after Number of iterations + 4 cycles. The latency is displayed on the block mask.

When you set the Number of iterations source parameter to

Property, the block shows the latency immediately. When you set

Number of iterations source to Auto, the block

calculates the latency based on the input port data type and displays the latency when you

update the model.

When you set the Number of iterations source parameter to

Auto, the number of iterations is input WL − 1, and

the latency is input WL + 3. If the input is of data type

double or single, the number of iterations is 16,

and the latency is 20.

Note

When you set the Scaling method parameter to

Multipliers, the block latency increases by four

cycles.

Performance was measured for the default configuration, with output scaling disabled and

fixdt(1,16,12) input. When the generated HDL code is synthesized into

a Xilinx® ZC706 (XC7Z045FFG900-2) FPGA, the design achieves 350 MHz

clock frequency. It uses the following

resources.

| Resource | Number Used |

|---|---|

| LUT | 891 |

| FFS | 899 |

Xilinx LogiCORE® DSP48 | 0 |

| Block RAM (16K) | 0 |

| Critical path | 2.792 ns |

When you use a multiplier for the CORDIC gain scaling, the design uses one DSP block and has a shorter critical path. The critical path difference is not significant at this number of bits, but as the size of the data increases, the critical path of the CSD implementation rises faster than the critical path of the multiplier.

| Resource | Number Used |

|---|---|

| LUT | 808 |

| FFS | 956 |

Xilinx LogiCORE DSP48 | 1 |

| Block RAM (16K) | 0 |

| Critical path | 2.574 ns |

Performance of the synthesized HDL code varies depending on your target and synthesis options. When you use vector input, the resource usage is about VectorSize times the scalar resource usage.

Extended Capabilities

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration option that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

This block supports code generation for complex signals.

Version History

Introduced in R2014bBefore R2022a, this block was named Complex to Magnitude-Angle HDL Optimized and was included in the DSP System Toolbox™ DSP System Toolbox HDL Support library.

In previous releases, the block implemented the CORDIC gain for hardware by using

shift-and-add logic. To use a multiplier, set the Scaling method

parameter to Multipliers. To use shift-and-add logic, set this

parameter to Shift-Add.

The block accepts and returns a column vector of elements that represent samples in time. The input vector can contain up to 64 samples.

See Also

Complex to Magnitude-Angle (Simulink) | dsphdl.ComplexToMagnitudeAngle | atan2

Topics

- HDL QAM Transmitter and Receiver (Communications Toolbox)

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)