Symbol Modulator

Libraries:

Wireless HDL Toolbox /

Modulation

Description

The Symbol Modulator block modulates data bits to complex data symbols. The block accepts data bits, along with a control signal, and outputs a modulated complex symbol with a valid signal. Each complex symbol comprises a standard number of bits based on the modulation type, as shown in this table. The modulation order specifies the number of points in the signal constellation.

| Modulation Type | Number of Bits Per Symbol (NBPS) | Modulation Order |

|---|---|---|

| BPSK | 1 | 2 |

| QPSK | 2 | 4 |

| 8-PSK | 3 | 8 |

| 16-PSK | 4 | 16 |

| 16-QAM | 4 | 16 |

| 32-PSK | 5 | 32 |

| 64-QAM | 6 | 64 |

| 256-QAM | 8 | 256 |

| 1024-QAM | 10 | 1024 |

| 4096-QAM | 12 | 4096 |

The block supports both scalar and vector inputs when you set the Modulation

source parameter to Property. It supports only scalar

input when you set the Modulation source parameter to Input

port. You can use this block to develop transmitters in a digital

communication system. The block provides an architecture suitable for HDL code generation and

hardware deployment.

Examples

Ports

Input

Data bits, specified as a scalar or a column vector.

Input data bits must be a multiple of NBPS, where NBPS is number of bits per symbol. If the specified input data bits are a nonmultiple of NBPS, the block ignores the input with insufficient or excessive bits.

When you set the Modulation source parameter to

Property:

For a scalar input, the data type must be

Boolean,fixdt(0,1,0), orfixdt(0,NBPS,0).For a vector input, the data type must be

Booleanorfixdt(0,1,0). The dimension of the vector must be NBPS-by-1.

When you set the Modulation source parameter to

Input port, for scalar input, the data type must be

Boolean or fixdt(0,1,0). This parameter

setting does not support vector input.

Data Types: Boolean | unsigned fixed point

Control signal that indicates if the input data is valid. When this value is

1 (true), the block accepts the values on the

data input port. When this value is 0

(false), the block ignores the values on the data input

port.

Data Types: Boolean

Modulation array index, specified as an integer. This value must be corresponding

to the index of the Modulation array parameter. For HDL code

generation, specify the value in the fixdt(0,4,0) format.

For example, if the Modulation array parameter is specified

as {"QPSK","BPSK,"16-QAM"} and you want the block to perform in

this sequence: BPSK, 16-QAM, BPSK, and QPSK, then you have to specify the

modArrIdx values in the order 1,

2, 1, and 0, respectively.

Here, the indices values 0, 1, and

2 correspond to QPSK, BPSK, and 16-QAM, respectively.

If you specify a value that exceeds the index of the modulation types specified in the Modulation array parameter, the block displays a warning message and:

Applies the first-specified modulation in the Modulation array parameter, when load is

1(true).Continues with the previous modulation when load is

0(false).

Dependencies

To enable this port, set the Modulation source parameter to

Input port.

Data Types: double | single | fixdt(0,4,0)

Modulation control signal to sample modulation, specified as a

Boolean scalar.

When this value is 1 (true), the block applies the modulation

based on the modArrIdx value. When this value is

0 (false), the block ignores any changes in the modArrIdx value and continues with the previous modulation

until this value changes to 1 (true).

If the load value changes to 1 (true)

during the block operation, the block resynchronizes and restarts modulation using the

current value of modArrIdx. This restart occurs

whether or not the modArrIdx value has

changed.

For example, if the block is operating in 256-QAM mode and the

load value changes to 1 (true) after four of

the eight required input bits are sent into the block, the block discards those first

four bits and restarts its operation from the fifth bit.

If you do not apply the load value as 1

(true) at the start of block operation, by default, the block applies the

first-specified modulation in the Modulation array

parameter.

Dependencies

To enable this port, set the Modulation source parameter to

Input port.

Data Types: Boolean

Clear internal states, specified as a Boolean scalar. When this

value is 1, the block stops the current calculation and clears all

internal states.

Dependencies

To enable this port, set the Modulation source parameter to

Property and then select the Enable reset

input port parameter.

Data Types: Boolean

Output

Modulated complex data symbols, returned as a complex scalar.

The block supports double and

single data types for simulation, but not for HDL code

generation.

For HDL code generation, set the Output data type parameter

to Custom and specify the word length.

Data Types: single | double | fixed point

Complex Number Support: Yes

Control signal that indicates if data from the data output

port is valid. When this value is 1 (true), the block returns valid

data on the data output port. When this value is

0 (false), the values on the data output

port are not valid.

Data Types: Boolean

Parameters

Main

To specify the modulation type by using the Modulation

parameter, select Property. To specify the modulation type

through the modArrIdx port during run time, select

Input port.

Select the modulation type.

Dependencies

To enable this parameter, set the Modulation source

parameter to Property.

Specify the modulation types as a string in a cell-array format. The supported modulation types are: BPSK, QPSK, 8-PSK, 16-PSK, 16-QAM, 32-PSK, 64-QAM, 256-QAM, 1024-QAM, and 4096-QAM.

Dependencies

To enable this parameter, set the Modulation source

parameter to Input port.

Select the type of constellation ordering as Default or

User-defined.

Specify the constellation mapping as a row vector. The row vector must contain unique elements in the range [0, (M – 1)], where M is the modulation order. The dimension of the vector must be 1-by-M.

For QAM modulations, the first element corresponds to the upper-left point of the

constellation, with subsequent elements running down column-wise from left to right.

If you set the Modulation parameter to

16-QAM, the modulation order is 16 and the vector

dimension is 1-by-16. The vector must contain unique elements in the range [0,

15].

Example: [0 1 3 2 4 5 7 6 12 13 15 14 8 9 11 10]

For PSK modulations, the first element correlates to the constellation point

corresponding to angle specified in the Phase offset (rad)

parameter, with subsequent elements running counter-clockwise .If you set the

Modulation parameter to 8-PSK, the

modulation order is 8 and the vector dimension is 1-by-8. The vector must contain

unique elements in the range [0, 7].

Example: [0 1 3 2 6 7 5 4]

Dependencies

To enable this parameter, set the Modulation source

parameter to Property and then set the

Constellation ordering type parameter to

User-defined.

Specify the constellation mapping array as a row vector in a cell array. The size of the cell array must be equal to the size of the modulation array.

Dependencies

To enable this parameter, set the Modulation source

parameter to Input port and then set the

Constellation ordering type parameter to

User-defined.

Select the phase offset. This parameter is applicable only for PSK modulation types, BPSK, QPSK, 8-PSK, 16-PSK, and 32-PSK.

Dependencies

To enable this parameter, set the Modulation source

parameter to Property and set the

Modulation parameter to BPSK,

QPSK, 8-PSK,

16-PSK, or 32-PSK.

Select the type of phase offset as Default or

User-defined.

Dependencies

To enable this parameter, set the Modulation source

parameter to Input port.

Specify the phase offset array. The supported phase offset values are:

pi, pi/2, pi/4,

pi/8, pi/16, pi/32,

0, -pi/2, -pi/4,

-pi/8, -pi/16, and -pi/32.

This parameter is applicable for PSK modulations only.

Note

If you specify 16-QAM, 64-QAM, 256-QAM, 1024-QAM, or 4096-QAM in the

Modulation array, you have to specify 0 in

the Phase offset array (rad) parameter for each QAM.

Dependencies

To enable this parameter, set the Modulation source

parameter to Input port and then set the Phase

offset type parameter to

User-defined.

Select how the block scales the signal constellation.

Minimum distance between symbols— Enables you to normalize the constellation by specifying the minimum distance between the constellation points using the Minimum distance parameter.Average power— Normalizes the constellation to average power using the Average power, referenced to 1 ohm (watts) parameter.

Dependencies

To enable this parameter:

Set the Modulation source parameter to

Input port. OrSet the Modulation source parameter to

Propertyand then set the Modulation parameter to16-QAM,64-QAM,256-QAM,1024-QAM, or4096-QAM.

Specify the minimum distance between the symbols as a positive scalar in the range from 1/32 to 1/8.

Dependencies

To enable this parameter:

Set the Modulation source parameter to

Input portand then set the Normalization method parameter toMinimum distance between symbols. OrSet the Modulation source parameter to

Property, set the Modulation parameter to16-QAM,64-QAM,256-QAM,1024-QAM, or4096-QAM, and then set the Normalization method parameter toMinimum distance between symbols.

Specify the average power of the symbols in the constellation as a positive scalar in the range 1/32 to 10. Power values assume a nominal impedance of 1 ohm.

Dependencies

To enable this parameter:

Set the Modulation source parameter to

Input portand then set the Normalization method parameter toAverage power. OrSet the Modulation source parameter to

Property, set the Modulation parameter to16-QAM,64-QAM,256-QAM,1024-QAM, or4096-QAM, and then set the Normalization method parameter toAverage power.

Select this parameter to enable the reset input port.

Dependencies

To enable this parameter, set the Modulation source

parameter to Property.

Data Types

Select the data type for the output data.

double and single data types

are supported for simulation. For simulation and HDL code generation, set this value

to Custom.

Specify the output word length. This value must be an integer in the range from 3 to 32.

Dependencies

To enable this parameter, set the Output data type

parameter to Custom.

Algorithms

The latency of the block varies with the type of input: scalar or vector and the

modulation source: Property or Input

port.

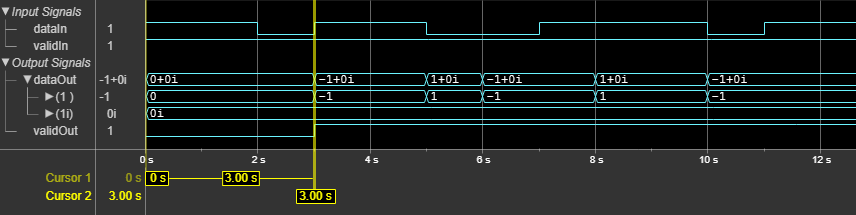

This figure shows a sample output and latency of the Symbol Modulator

block when you specify a scalar input, set the Modulation source

parameter to Property, set the Modulation

parameter to BPSK, and use the default settings for the other

block parameters.

The latency of the block is equal to NBPS + 2 clock cycles. This calculation shows that the latency of the block is 3 clock cycles, as shown in this figure.

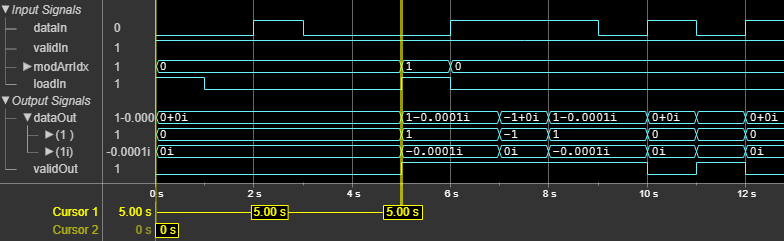

This figure shows a sample output and latency of the Symbol Modulator

block when you specify a scalar input, set the Modulation source

parameter to Input port, set the Modulation

array to {"BPSK","QPSK"}, and use the default settings for

the other block parameters. The latency of the block is equal to NBPS +

4 clock cycles. The NBPS value corresponds to the modulation array

index specified through the modArrIdx port. This calculation shows

that the latency of the block is 5 clock cycles, as shown in this figure.

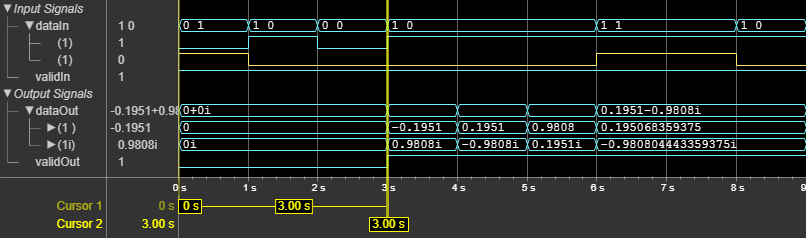

This figure shows a sample output and latency of the Symbol Modulator

block when you specify a vector input, set the Modulation source

parameter to Property, set the Modulation

parameter to QPSK, and use the default settings for the other

block parameters. The latency of the block is 3 clock cycles, as shown in this

figure.

The performance of the synthesized HDL code varies with the target and synthesis options. It also varies based on the selected modulation type and output data type.

This table shows the resource and performance data synthesis results of the block when

you set the Modulation source parameter to Input

port, specify the Modulation array parameter as

{"BPSK", "QPSK", "16-QAM", "64-QAM", "256-QAM", "1024-QAM",

"4096-QAM"}, and use the default settings for the other block parameters. The

generated HDL is targeted to an AMD®

Zynq®

UltraScale+™ MPSoC ZCU102 Evaluation Board. The design achieves a clock frequency of 695.66

MHz.

| Resource | Number Used |

|---|---|

| Slice LUTs | 221 |

| Slice Registers | 135 |

| DSPs | 0 |

| BRAM | 3 |

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2025a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)