Generate HDL Code and Perform Synthesis Using Cadence Genus on ASIC Devices

This example shows how to generate and synthesize HDL code for generic ASIC devices using the HDL Workflow Advisor and the Cadence® Genus synthesis tool. This example shows you how to use either the default synthesis settings or you own custom synthesis settings. For the default synthesis settings, HDL Workflow Advisor provides the required synthesis Tcl file. For the custom synthesis settings, you must provide a custom setup Tcl file, constraints SDC files, and synthesis Tcl files.

Requirements

HDL Coder™

Red Hat® Linux release 8.9

Cadence Genus version 21.18

Set Synthesis Tool Path

Set the Cadence Genus synthesis tool path to MATLAB® path using the hdlsetuptoolpath command:

hdlsetuptoolpath('ToolName','Cadence Genus','ToolPath',... installation_path);

Where installation_path is the path to the Cadence Genus synthesis tool version supported in the current release, see HDL Language Support and Supported Third-Party Tools and Hardware.

Open Model and Generate HDL Code

To open and generate HDL code for the Simulink model using the HDL Workflow Advisor, follow these steps:

1. Open the example hdlcoder_led_blinking model, which is compatible for HDL code generation. To open this model, in the MATLAB command prompt, enter:

open_system('hdlcoder_led_blinking');

2. In the Apps tab, click HDL Coder. Then, in the HDL Code tab, click Workflow Advisor.

3. In the HDL Workflow Advisor, in the 1.1. Set Target Device and Synthesis Tool task, set Target workflow to Generic ASIC/FPGA and the Synthesis Tool to Cadence Genus. Then, click Run This Task.

4. In the 1.2 Set Target Frequency task, set Target frequency (MHz) to 50. For more information, see Target Frequency.

5. In the 2.1. Check Model Settings task, click the HDL Code Advisor to run additional compatibility checks. After making changes, click Apply, and then click Run This Task.

6. In the 3.1 Set HDL Options task, set the HDL options using the HDL Code Generation Settings. For example, to customize the target HDL language and the target code generation folder, use the Set HDL Options task. After making changes, click Apply.

7. In the 3.2. Generate RTL Code and Testbench task, select the Generate RTL code and Generate test bench options. Then, click Run This Task.

Synthesize HDL Code

You can choose to use either the default synthesis settings or custom synthesis settings.

Synthesize HDL Code Using Default Settings

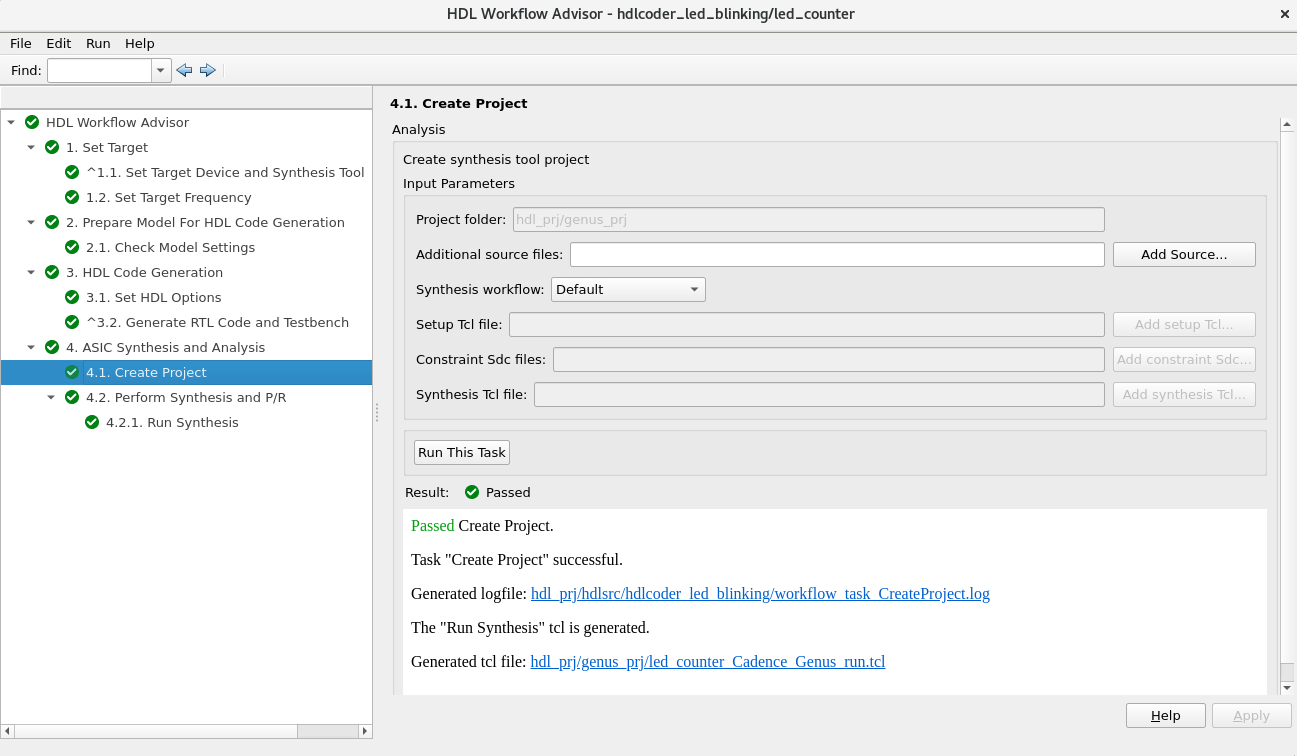

In the 4. ASIC Synthesis and Analysis > 4.1 Create Project task, set the Synthesis workflow to Default. When you select default synthesis workflow, the Setup Tcl file, Constraints Sdc files and Synthesis Tcl file options are dimmed. Then, click Run This Task. To view the generated log file and TCL file, click the HTML links in the Result pane.

The HDL Workflow Advisor generates this Tcl script file:

# HDL Coder Downstream Integration Tcl Script set myTool "Cadence Genus 21.18" set myProject "" set myProjectFile "" set myTopLevelEntity "led_counter" #------------------------------------------------------------------------------- #Info and initial setup #------------------------------------------------------------------------------- #------------------------------------------------------------------------------- #Library setup #------------------------------------------------------------------------------- set_db library tutorial.lib set_db syn_global_effort low set_db super_thread_servers "localhost" set_db st_launch_wait_time 1 #------------------------------------------------------------------------------- # Add HDL source files puts "### Update $myTool project with HDL source files" read_hdl -language vhdl ../hdlsrc/hdlcoder_led_blinking/led_counter_pkg.vhd read_hdl -language vhdl ../hdlsrc/hdlcoder_led_blinking/led_counter.vhd elaborate ${myTopLevelEntity} #------------------------------------------------------------------------------- #3 Constraints #------------------------------------------------------------------------------- create_clock -name MWCLK -period 20.000 [get_ports clk] #------------------------------------------------------------------------------- #4 Synthesis #------------------------------------------------------------------------------- syn_generic syn_map report_timing > ./reports/timing.txt report_gates > ./reports/gates.txt exit puts "### Synthesis Complete."

Synthesize HDL Code Using Custom Settings

To synthesize HDL code using custom settings, in the 4.1 Create Project task, set the Synthesis workflow to Custom, and specify the Setup Tcl file, Constraints Sdc files and Synthesis Tcl file parameters. For more information, see Create Project.

Use this sample code for a custom setup Tcl file:

# custom setup tcl file #------------------------------------------------------------------------------- #1 Info and initial setup #------------------------------------------------------------------------------- #------------------------------------------------------------------------------- #2 Library setup #------------------------------------------------------------------------------- set_db library tutorial.lib set_db syn_global_effort low set_db super_thread_servers "localhost" set_db st_launch_wait_time 1 #-------------------------------------------------------------------------------

Use this sample code for a custom constraint SDC file.

# Custom constraint Sdc file #------------------------------------------------------------------------------- #3 Constraints #------------------------------------------------------------------------------- create_clock -name MWCLK -period 20.000 [get_ports clk]

Use this sample code for a custom synthesis Tcl file.

#------------------------------------------------------------------------------- #4 Synthesis #------------------------------------------------------------------------------- syn_generic syn_map report_timing > ./reports/timing.txt report_gates > ./reports/gates.txt exit puts "### Synthesis Complete."

To view the generated log file and Tcl file, click the HTML links in the Result pane.

The HDL Workflow Advisor integrates the individual files and generates this Tcl script:

# HDL Coder Downstream Integration Tcl Script set myTool "Cadence Genus 21.18" set myProject "" set myProjectFile "" set myTopLevelEntity "led_counter" #------------------------------------------------------------------------------- #1 Info and initial setup #------------------------------------------------------------------------------- #------------------------------------------------------------------------------- #2 Library setup #------------------------------------------------------------------------------- set_db library tutorial.lib set_db syn_global_effort low set_db super_thread_servers "localhost" set_db st_launch_wait_time 1 #------------------------------------------------------------------------------- # Add HDL source files puts "### Update $myTool project with HDL source files" read_hdl -language vhdl ../hdlsrc/hdlcoder_led_blinking/led_counter_pkg.vhd read_hdl -language vhdl ../hdlsrc/hdlcoder_led_blinking/led_counter.vhd elaborate ${myTopLevelEntity} #------------------------------------------------------------------------------- #3 Constraints #------------------------------------------------------------------------------- create_clock -name MWCLK -period 20.000 [get_ports clk] #------------------------------------------------------------------------------- #4 Synthesis #------------------------------------------------------------------------------- syn_generic syn_map report_timing > ./reports/timing.txt report_gates > ./reports/gates.txt exit puts "### Synthesis Complete."

Run Build Process

To perform synthesis using the Cadence Genus synthesis tool, run the build process. You can run the build process in the HDL Workflow Advisor or run it externally.

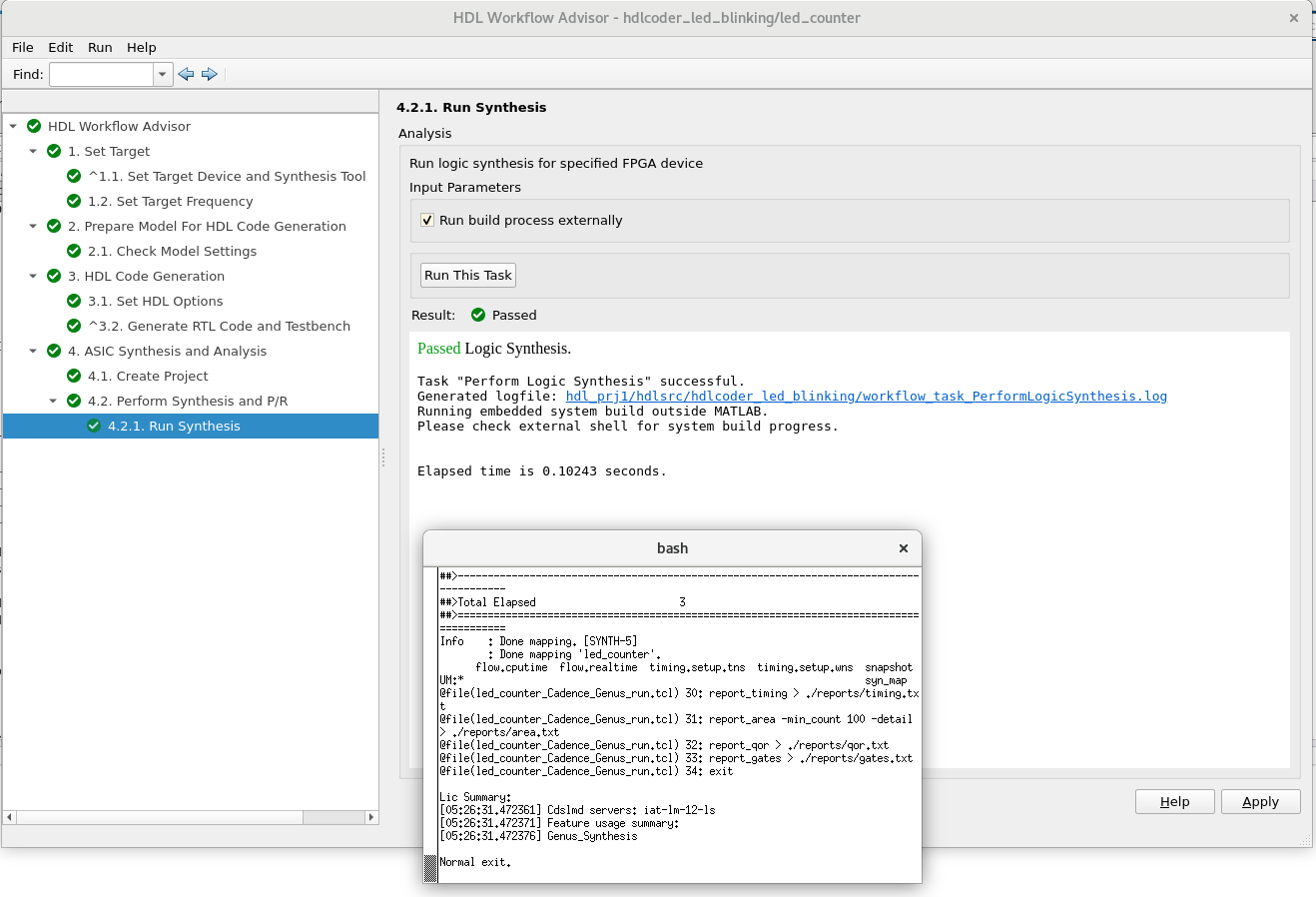

To run the build process in the HDL Workflow Advisor, in the 4.2.1 Run Synthesis task, clear the Run build process externally option. The synthesis runs in the same console, and you cannot use MATLAB until the synthesis process is completed.

The Result pane displays a synthesis log and provides links to the Parsed power report file and Parsed resource file. To view the resource report and power report, click the HTML links in the Result pane.

To perform the synthesis in an external console, in the 4.2.1 Run Synthesis task, select Run build process externally. This option allows the build process to run in an external console, so you can continue using MATLAB while synthesis is in progress.

Additionally, you can generate a MATLAB® script to execute the HDL Workflow Advisor tasks from the MATLAB® command prompt by exporting the HDL Workflow Advisor settings to a script. In the HDL Workflow Advisor pane, navigate to File > Export to Script. In the Export Workflow Configuration dialog box, enter a file name and save the script. For mode informations, see Run HDL Workflow with a Script.