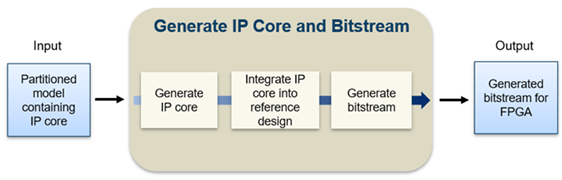

Generate an IP Core and Bitstream

The IP core is a shareable and reusable HDL component that implements a specific function, typically an algorithm. An IP core consists of IP core definition files, HDL code generated for your algorithm, a C header file containing the register address map, and the IP core report.

By using the IP Core Generation workflow in the HDL Workflow

Advisor, HDL Coder™ can generate an IP core that contains the HDL source code and the C header

files for integrating the IP core into your Vivado® project, and then program the target hardware. You can integrate the IP core

into a default or custom reference design depending on the target platform, and generate a

bitstream to be deployed to your FPGA hardware. The input is a designed IP core in a

Simulink® model or MATLAB® function. The output is a bitstream generated by HDL Coder from the IP core.

Categories

- Custom IP Core Generation

Generate HDL IP core from your DUT for deployment to the default system reference design or custom reference design registered with the board

- Reference Design Integration and Deployment

Integrate the generated IP core into the default system reference design

- Custom Board and Reference Design

Integrate generated IP core into a target SoC device by defining a custom board and reference design