dsphdl.FIRDecimator

Finite impulse response (FIR) decimation filter

Description

The dsphdl.FIRDecimator

System object™ implements a single-rate polyphase FIR decimation filter that is optimized for

HDL code generation. The object provides a hardware-friendly interface with input and output

control signals. To provide a cycle-accurate simulation of the generated HDL code, the object

models architectural latency including pipeline registers and resource sharing.

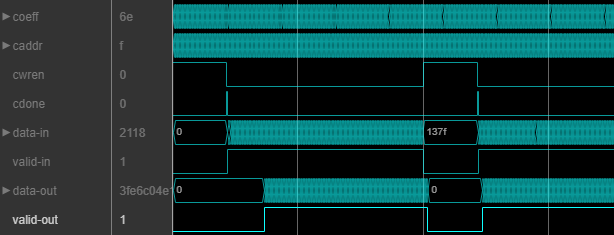

The object accepts scalar or vector input. When you use vector input and the vector size is less than the decimation factor, the decimation factor must be an integer multiple of the vector size. In this case, the output is scalar and an output valid signal indicates which samples are valid after decimation. The output data is valid every DecimationFactor/VectorSize samples. The waveform shows an input vector of four samples and a decimation factor of eight. The output data is a scalar that is valid every second cycle.

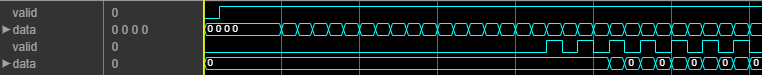

When you use vector input and the vector size is greater than the decimation factor, the vector size must be an integer multiple of the decimation factor. In this case, the output is a vector of VectorSize/DecimationFactor samples. The waveform shows an input vector of eight samples and a decimation factor of four. The output data is a vector of two samples on every cycle.

The object provides two filter structures. The direct form systolic architecture provides an implementation that makes efficient use of Intel® and Xilinx® DSP blocks. This architecture can be fully parallel or serial. To use a serial architecture, the input samples must be spaced out with a regular number of invalid cycles between the valid samples. The direct form transposed architecture is a fully parallel implementation and is suitable for FPGA and ASIC applications. For a filter implementation that matches multipliers, pipeline registers, and pre-adders to the DSP configuration of your FPGA vendor, specify your target device when you generate HDL code.

For scalar input, all filter structures optimize hardware resources by sharing multipliers for symmetric or antisymmetric filters and by removing the multipliers for zero-valued coefficients such as in half-band filters and Hilbert transforms. When your input is a vector, the filter structure removes the multipliers for zero-valued coefficients but does not optimize for symmetric coefficients.

The object implements one filter for each sample in the input vector. The object then shares this filter between the polyphase subfilters by interleaving the subfilter coefficients in time.

Note

The output of the dsphdl.FIRDecimator object does not match the output from the

dsp.FIRDecimation object sample-for-sample. This difference is mainly

because of the phase that the samples are applied across the subfilters. To match the

dsp.FIRDecimation object, apply DecimationFactor – 1

zeroes to the dsphdl.FIRDecimator object at the start of the data stream.

The dsp.FIRDecimation object also uses slightly different default data

types than the dsphdl.FIRDecimator object.

To filter and decimate input data with an HDL-optimized algorithm:

Create the

dsphdl.FIRDecimatorobject and set its properties.Call the object with arguments, as if it were a function.

To learn more about how System objects work, see What Are System Objects?

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a MATLAB® script, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the System object.

Creation

Syntax

Description

firDecim = dsphdl.FIRDecimator

firDecim = dsphdl.FIRDecimator(dec,num) sets the DecimationFactor property to dec and the Numerator property to

num.

firDecim = dsphdl.FIRDecimator(___,PropertyName=Value)FilterStructure='Direct form transposed' specifies the filter

architecture as a fully parallel implementation that is suitable for FPGA and ASIC

applications.

Properties

Usage

Syntax

Description

[

filters data using the coefficients dataOut,validOut]

= firDecim(dataIn,validIn,coeff)coeff. Use this syntax when you

set the NumeratorSource property to 'Input port (Parallel

interface)'. For example:

firDecim = dsphdl.FIRDecimator(NumeratorSource='Input Port (Parallel interface)') Numerator = myGetNumerator(); % calculate coefficients for k=1:length(dataIn) [dataOut(x),validOut(x++)] = firDecim(dataIn(k),validIn(k),Numerator);

[

loads the coefficient value dataOut,validOut]

= firDecim(dataIn,validIn,coeff,caddr,cwren,cdone)coeff to the caddr

memory location, when cwren is 1

(true). Set cdone to 1

(true) along with the last coefficient write, or after you finish

writing coefficients. The object ignores any input data provided when

cwren is 1 (true), but still

returns dataOut with validOut until it clears

the filter pipeline. Use this syntax when you set the NumeratorSource

property to 'Input port (Memory interface)'. For example:

firDecim = dsphdl.FIRDecimator(NumeratorSource='Input Port (Memory interface)') ... for k=1:length(Numerator) [dataOut(x),validOut(x++)] = firDecim(0,0,Numerator(k),k,true,(k==length(Numerator)); for k=1:length(dataIn) [dataOut(x),validOut(x++)] = firDecim(dataIn(k),validIn(k),0,0,false,false);

[

filters data when dataOut,validOut]

= firDecim(dataIn,validIn,reset)reset is false. When

reset is true, the object resets the filter

registers. The object expects the reset argument only when you set

the ResetInputPort property to true.

For more reset considerations, see the Reset Signal section on the Hardware Control Signals page.

Input Arguments

Output Arguments

Object Functions

To use an object function, specify the

System object as the first input argument. For

example, to release system resources of a System object named obj, use

this syntax:

release(obj)

Algorithms

This System object implements the algorithms described on the FIR Decimator block reference page.