HDL Interleaver and Deinterleaver

This example shows how to design block interleaver and block deinterleaver blocks and implement interleaving and deinterleaving in a communication system using these blocks.

Interleaving

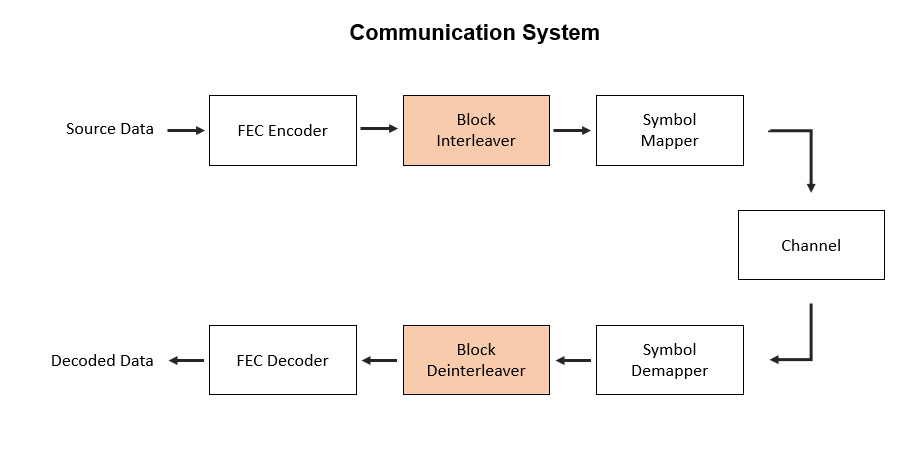

Audio processing and radio transmission applications are often affected due to burst noise. Burst noise degrades the performance of forward error correction (FEC) codes. This degradation of performance results in the form of errors in the decoded data. Interleaving is a technique that spreads out the continuous burst of errors and improves data decoding using FEC codes. Interleaving is part of wireless standards such as digital video broadcasting - satellite-second generation (DVB-S2), wireless local area network (WLAN 802.11), and long term evolution (LTE). This block diagram shows the overview of a communication system with interleaver and deinterleaver.

An interleaver writes the input data in a row-wise format to the memory and reads the output data in a column-wise format from the memory. A deinterleaver operates in the reverse manner by writing the input data in a column-wise format to the memory and reading the output data in a row-wise format from the memory. The number of rows and columns decide the extent of interleaving. This figure shows the working of a block interleaver and block deinterleaver, each with four rows and four columns.

HDL Interleaver Model

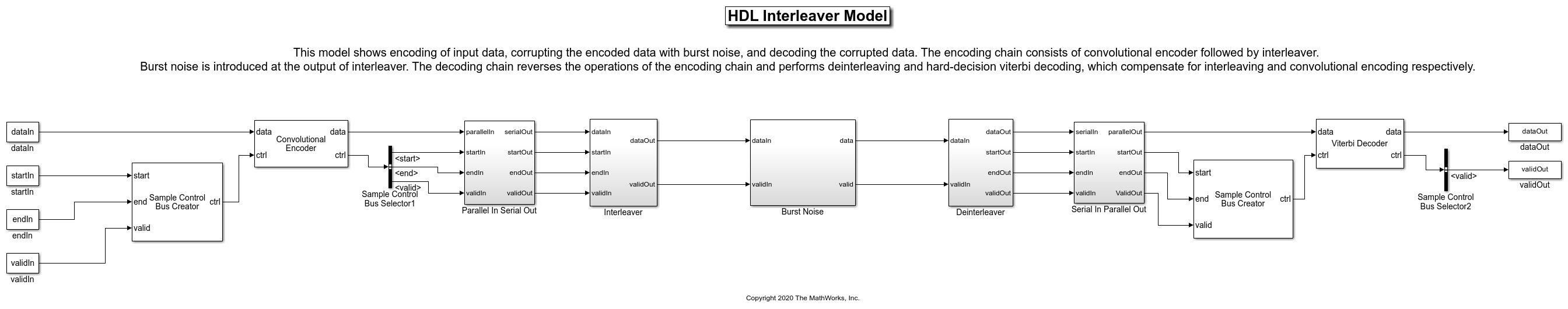

This section provides the overview of a communication system implemented using the WHDLInterleaverModel.slx model, which contains interleaver and deinterleaver blocks. The input data to the model, dataIn, is convolutionally encoded using the Convolutional Encoder block. The encoded data is then interleaved by the Interleaver Block that is in the Interleaver subsystem. Burst noise is added to the interleaved data by performing a XOR operation of the data with the burst noise. The corrupted data is given as an input to the Deinterleaver subsystem where the Deinterleaver Block spreads out the burst errors in the data. The Viterbi Decoder block decodes the deinterleaved data and outputs the final decoded data. The model contains additional subsystems that are used to synchronize the blocks in the model. A constant block with the interleave variable is provided in the Interleaver and Deinterleaver subsystems of the model. You can set or reset the interleave variable to enable or disable interleaving.

Port Description

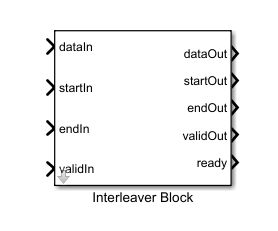

This section explains the input and output ports of the Interleaver Block that is in the Interleaver subsystem of the WHDLInterleaverModel.slx model.

Input Ports:

dataIn — Input data to be interleaved. As the block performs serial processing, dataIn is specified as a scalar. The block supports

double,single,Boolean,integer, andfixed pointdata types.startIn — Start signal of the input data block, specified as a Boolean scalar.

endIn — End signal of the input data block, specified as a Boolean scalar.

validIn — Valid signal of the input data block, specified as a Boolean scalar.

Output Ports:

dataOut — Interleaved output data returned as a scalar. The output data type is same as that of the dataIn port.

startOut — Start signal of the output data block, returned as a Boolean scalar.

endOut — End signal of the output data block, returned as a Boolean scalar.

validOut — Valid signal of the output data block, returned as a Boolean scalar.

ready — Ready output signal used for external interfacing, returned as a Boolean scalar. The interleaver accepts one new block of input data while still processing an earlier data block. If more than one block of data is given as input while processing an earlier data block, the ready signal deasserts, indicating that the interleaver is not ready to accept new data.

The input and output ports of the Deinterleaver Block, which is in the Deinterleaver subsystem of the WHDLInterleaverModel.slx model, are the same as that of the Interleaver Block.

Parameters

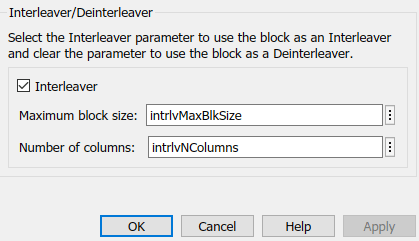

This figure shows the block mask of the Interleaver Block. You can use this block as an interleaver or a deinterleaver by modifying a parameter selection on the block mask.

The Interleaver Block supports these parameters:

Interleaver — Nontunable mask parameter. Select the Interleaver parameter to use the block as an Interleaver. Clear this parameter to use the block as a Deinterleaver.

Maximum block size — Nontunable mask parameter. This parameter specifies the maximum supported block size. This value sets the size of the RAM used inside the block. The minimum value of this parameter is 4.

Number of columns — Nontunable mask parameter. This parameter specifies the number of columns. The minimum number of columns is 2 and must be a factor of Maximum block size.

The block size of the interleaver is tunable, meaning it can be adjusted during the simulation by using the input start, end, and valid control signals. The block size is the number of input valid samples from the start to the end of the data block. The block size must be an integer multiple of Number of columns. The minimum value of the block size is Number of columns x 2 and the maximum value is Maximum block size.

For example, if you specify the Maximum block size parameter as 30 and the Number of columns parameter as 5, the possible values of the tunable block size during the simulation are 10, 15, 20, 25, and 30. The block automatically calculates the number of rows, which varies with the block size.

Architecture

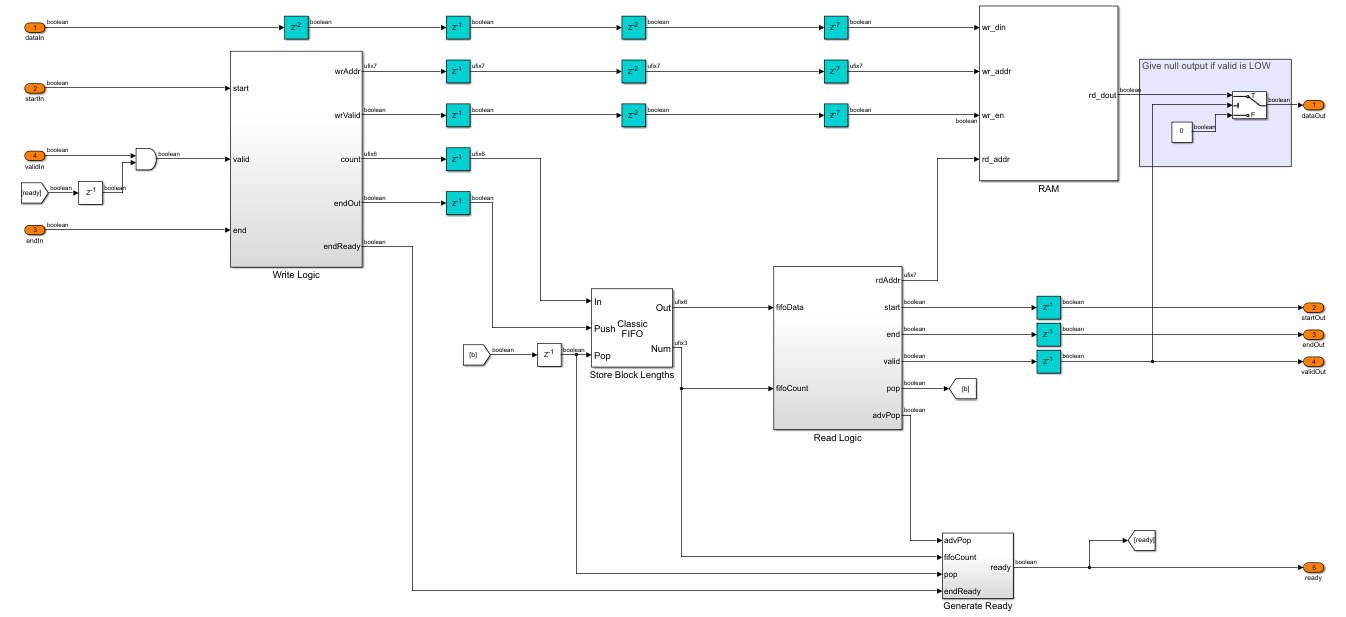

This section explains the architecture of the Interleaver Block. The Interleaver Block accepts the input data in the form of data blocks along with control signals. The Interleaver Block interleaves each data block independently. This figure shows the architecture of the Interleaver Block.

The Interleaver Block contains three subsystems and two blocks:

Write Logic — This subsystem accepts input control signals and generates appropriate write valid and write address signals for writing the data into the RAM.

Store Block Lengths — This is a FIFO block that stores the input data block lengths during the simulation.

Read Logic — This subsystem performs the actual interleaving operation and generates the read address to read out the data from the RAM.

Generate Ready — This subsystem generates the ready output signal for interfacing with other blocks.

RAM — This block stores the input data and outputs interleaved data based on the input read address.

Only the Generate Read Address subsystem in the Read Logic subsystem of the Interleaver Block and Deinterleaver Block differs in its functionality, remaining other subsystems are same.

Model Simulation

Run the runWHDLInterleaverModel.m script to simulate the WHDLInterleaverModel.slx model. The script initializes, simulates, and validates the outputs of the model. For optimum results, tune the interleaving parameters in the script based on the burst noise parameters.

Disable interleaving and then run the script to simulate the model, validate the outputs, and display errors.

errorRateWithoutInterleaving =

0.1354

Enable interleaving and then run the script to simulate the model, validate the outputs, and display errors.

errorRateWithInterleaving =

0.0125

When you enable interleaving, the error rate is less than the error rate when you disable interleaving. This result occurs because interleaving improves the performance of the Viterbi Decoder block by spreading out the burst errors.

HDL Code Generation and Implementation Results

To check and generate the HDL code referenced in this example, you must have the HDL Coder™ product. To generate the HDL code, enter this command at the MATLAB command prompt.

>> makehdl('WHDLInterleaverModel/Deinterleaver/Deinterleaver Block')

The resource utilization and frequency of operation values vary with the input data type, the maximum block size, and the number of columns. HDL code is synthesized for the Xilinx® Zynq®–7000 ZC706 evaluation board for the Deinterleaver Block in the Deinterleaver subsystem with fixdt(1,16,14) input, a maximum block size of 360, and 30 columns. This table shows the post place and route resource utilization. The maximum frequency of operation is 292 MHz. Similar results are obtained for the Interleaver Block in the Interleaver subsystem.

Resources Usage

_______________ _____

Slice Registers 293

Slice LUT 271

RAMB18 1