GMSK Modulator

Libraries:

Wireless HDL Toolbox /

Modulation

Description

The GMSK Modulator block modulates data bits using the Gaussian minimum shift keying (GMSK) method. The block supports scalar inputs and outputs modulated complex-valued scalar or column-vector data symbols along with valid and ready controls signals. The block enables you to use your bandwidth more effectively and helps reduce the problems caused by multipath fading and signal distortion.

You can use this block in applications such as global system for mobile communications (GSM), satellite communications, Bluetooth, military communications, tactical radios, drone control/command and missile communications. The block provides an interface and architecture suitable for HDL code generation and hardware deployment.

Examples

Modulate Data Bits into Symbols Using GMSK

Use GMSK Modulator block to modulate data bits to symbols by using GMSK method.

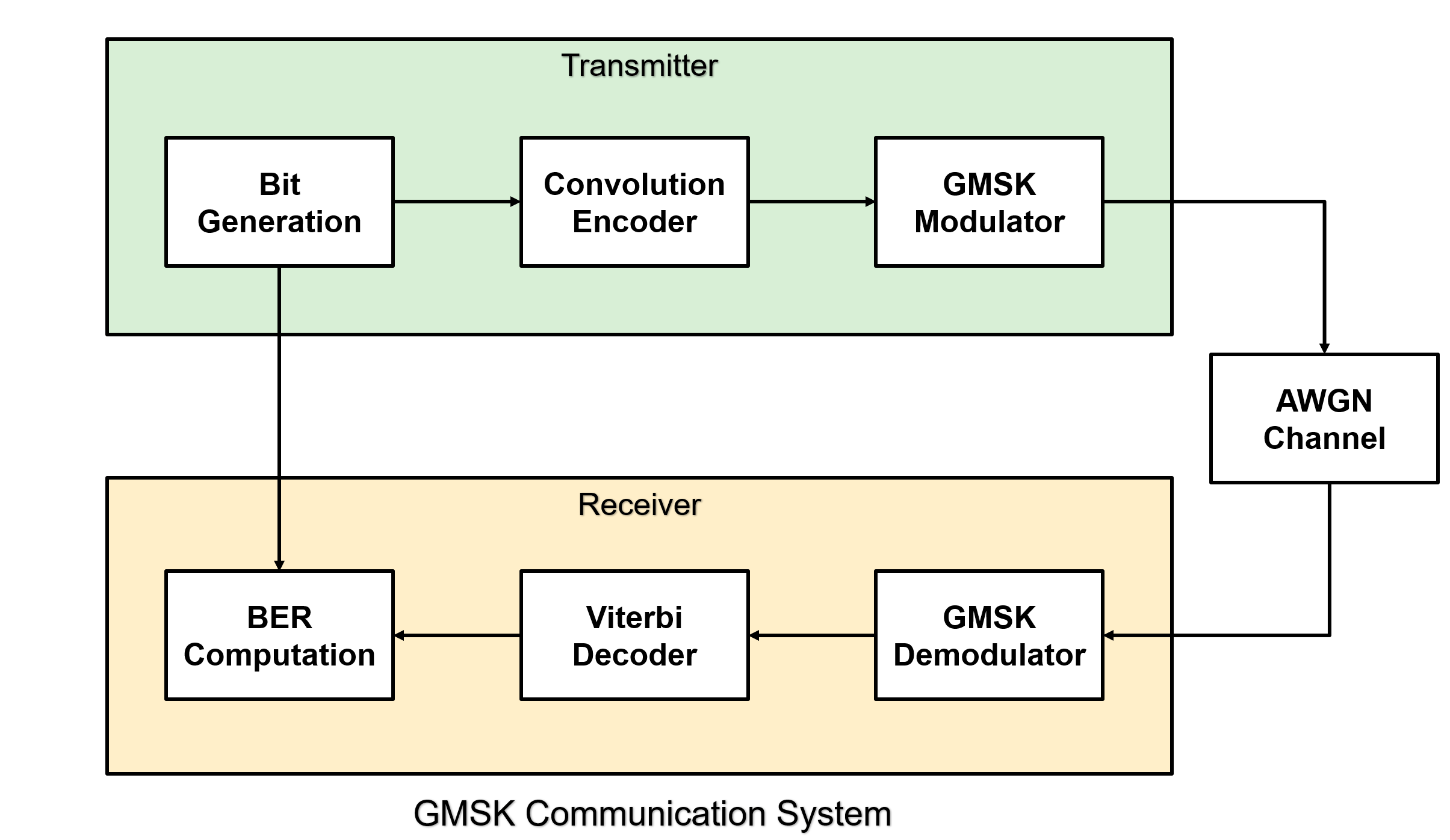

Recover Data Bits with GMSK Modulation and Demodulation

Convert data bits into modulated symbols and then recover the original bits through demodulation.

- Since R2026a

- Open Script

Accelerate BER Simulations of GMSK System Using FPGA-in-the-Loop Workflow

Accelerate BER simulations of GMSK system using FPGA-in-loop workflow.

- Since R2026a

- Open Live Script

Ports

Input

Data bits, specified as a Boolean scalar or ufix1.

For HDL code generation, the input data type must be ufix1 or

Boolean and the maximum output word length the block supports is

16 bits.

Data Types: Boolean | fixdt(0,1,0)

Indicates valid input data, specified as a Boolean scalar.

This port is a control signal that indicates when the sample from the

data input port is valid. When this value is

1, the block captures the values on the data

input port. When this value is 0, the block ignores the values on

the data input port.

Data Types: Boolean

Clear internal states, specified as a Boolean scalar. When this value is

1, the block stops the current calculation and clears all

internal states.

Dependencies

To enable this port, select the Enable reset input port parameter.

Data Types: Boolean

Output

Modulated complex output data symbols, returned as a complex-valued scalar or column vector.

When you set the Output type parameter to

Vector, the output is a vector of number of samples per symbol.When you set the Output type parameter to

Scalar, the output is a scalar.

Data Types: signed fixed point

Complex Number Support: Yes

Indicates valid output data, returned as a scalar.

This port is a control signal that indicates when the data

output port is valid. The block sets this value to 1 when the data

samples are available on the data output port.

Data Types: Boolean

Indicates block is ready, returned as a scalar.

This is a control signal that indicates when the block is ready for new input

data. When this value is 1, the block accepts input data in the

next time step. When this value is 0, the block ignores input data

in the next time step.

Dependencies

To enable this port, set the Output type parameter to

Scalar.

Data Types: Boolean

Parameters

Main

Product of the signal bandwidth and symbol time for the Gaussian pulse shape, specified as a positive scalar value.

Pulse length, specified as a positive integer. The pulse length value represents the length of the Gaussian pulse shape in symbol intervals.

Symbol prehistory, specified as a scalar or vector of –1s or 1s that the block uses before the start of the simulation.

For a scalar value, the block expands it to a vector of length L – 1, where L represents the pulse length. You can specify the L value using the Pulse length (symbol intervals) parameter.

For example, if you specify a scalar value

-1and if the Pulse length (symbol intervals) parameter is set to4, the block expands this value as[-1 -1 -1].For a vector value, the block considers the elements in the vector in a reverse chronological order. The vector length must be L – 1.

For example, if you specify a vector value

[-1 1 1]and if the Pulse length (symbol intervals) parameter is set to4, the block considers this value as[1 1 -1].

Phase offset of the modulated waveform in radians, specified as a numeric scalar in the range from –2*π to 2*π.

Number of samples per symbol, specified as a positive integer in the range 1 to 64. The number of samples per symbol represents the upsampling factor from input samples to output samples.

Number of data points to retrieve from the look-up table (LUT), specified as a positive integer and a power of 2. The maximum value the block supports is 65,536.

The recommended number of data points is 2 raised to the power of (Output word length – 2). You can modify this value based on your requirements. Increasing the number of data points improves the precision of the results. However, it is important to note that this increment also leads to higher utilization of LUTs and block RAMs (BRAMs), which could impact overall resource efficiency.

Specify the output type as Vector or

Scalar.

Data Type

Output word length, specified as a positive scalar with word length less than 16.

Control Port

Select this parameter to enable the reset input port.

Algorithms

The Bandwidth time product parameter represents bandwidth multiplied by time. This parameter reduces the bandwidth at the expense of increased intersymbol interference. The Pulse length (symbol intervals) parameter measures the length of the Gaussian pulse shape, in symbol intervals. Bb represents the bandwidth of the pulse and T is the symbol durations. Q(t) is the complementary cumulative distribution function.

The block generates the filter coefficients using these equations based on the parameters you select in the block mask of the example. The choice of Bandwidth time product parameter decides the performance of the modulator as the bit error rate can be expressed as a function of BT. For this block, an input symbol of 1 causes a phase shift of π/2 radians, which corresponds to a modulation index of 0.5.

The latency of the block is equal to Pulse length + 4 clock cycles.

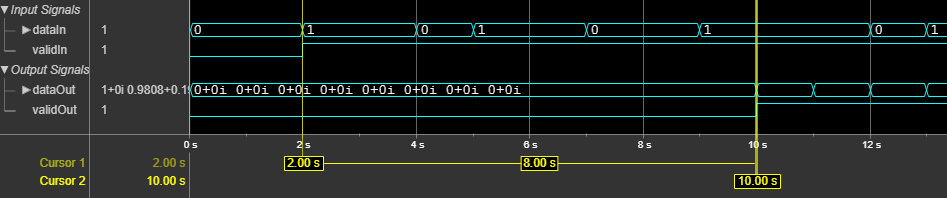

This figure shows a sample output and latency of the GMSK Modulator block for default configuration. The latency of the block is eight clock cycles.

The performance of the synthesized HDL code varies with your target and synthesis

options. The input data type used in this example for generating HDL code is

fixdt(0,1,0).

This table shows the resource and performance data synthesis results of the block, when

you set the Number of samples per symbol parameter to

4, the Pulse length (symbol intervals) parameter

to 8, the Number of data points parameter to

1024, and the Output word length parameter to

16. The generated HDL is targeted to the AMD®

Zynq®- 7000 ZC706 evaluation board.

| Output Type | Slice LUTs | Slice Registers | DSPs | Block RAMs | Maximum Frequency in MHz |

|---|---|---|---|---|---|

| Scalar | 462 | 389 | 0 | 2 | 259 |

| Vector | 476 | 245 | 0 | 2 | 276 |

This table shows the resource and performance data synthesis results of the block, when

you set the Number of samples per symbol parameter to

4, the Pulse length (symbol intervals) parameter

to 8, the Number of data points parameter to

16384, and the Output word length parameter to

16. The generated HDL is targeted to the AMD

Zynq- 7000 ZC706 evaluation board.

| Output Type | Slice LUTs | Slice Registers | DSPs | Block RAMs | Maximum Frequency in MHz |

|---|---|---|---|---|---|

| Scalar | 557 | 397 | 0 | 32 | 240 |

| Vector | 576 | 253 | 0 | 32 | 254 |

Increasing the number of data points improves the precision of the results. However, it is important to note that this increment also leads to higher utilization of look-up tables (LUTs) and block RAMs (BRAMs), which could impact overall resource efficiency. The standard LUT size is calculated as 2 raised to the power of (Output word length – 2). You can modify the value based on your requirements.

References

[1] Anderson, John B., Tor Aulin, and Carl-Erik Sundberg. Digital Phase Modulation. New York: Plenum Press, 1986.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2024a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)