Register Write

Write data to a register region on the specified IP core

Libraries:

SoC Blockset /

Processor I/O

Description

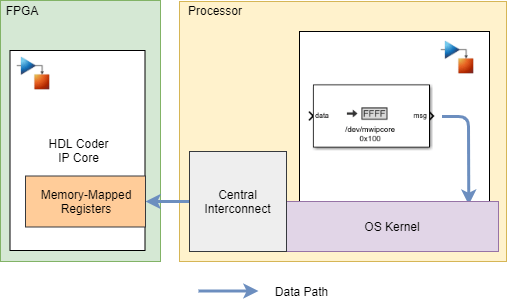

The Register Write block writes data from your processor algorithm to a register region on the specified IP core. In simulation, a timer-driven or event-driven task subsystem contains the Register Write block. The data signals from the Register Write block connect to the Register Channel block managing those registers and their transactions.

When developing or analyzing the software side of an SoC application, the Register Write block can be connected to an IO Data Sink block. In this configuration, the IO Data Sink block provides either previously recorded or artificial data, enabling a more directed simulation of the software and processor side of the application, without need to explicitly model the hardware and memory interactions.

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2019a