Specify and Verify Design Requirements

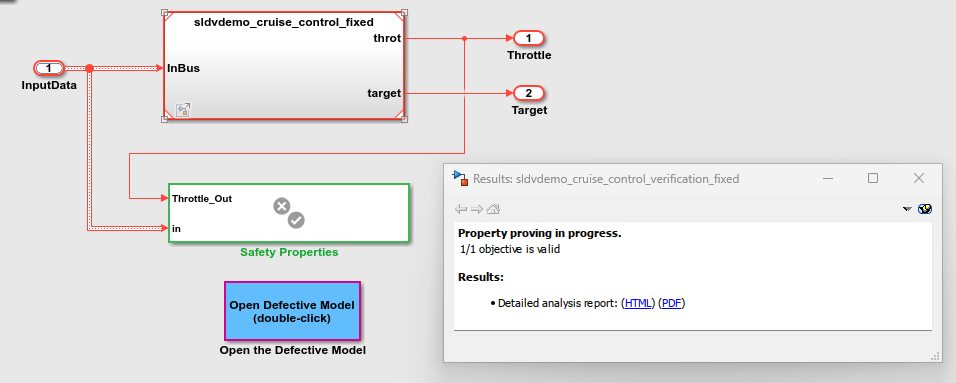

Safety requirements define undesired behaviors in a model. Simulink® Design Verifier™ uses property proving to verify that properties associated with model requirements hold under all possible input values or provides counterexamples that lead to violations. You use Simulink Design Verifier to model design requirements as properties and then Prove Properties in a Model.

Blocks

Functions

Topics

- Prove Model Properties

Workflow and techniques for proving model properties.

- Prove Properties in a Model

Prove model properties that you specify using a Proof Objective block.

- Debug Property Proving Violations by Using Model Slicer

Use Model Slicer to debug your design with assertion blocks.

- Prove System-Level Properties Using Verification Model

An example that uses a verification model to prove system-level properties.

- Property Proving Using Proof Objective Block

You can use Simulink® Design Verifier™ to model design requirements as properties and then prove properties in a model.

- Property Proving Using MATLAB Function Block

This example shows how to verify the seat belt reminder design model.

- Property Proving Using MATLAB Truth Table Block

This example shows how to verify the seat belt reminder design model referenced in the top block above.

- Property Proving with an Assumption Block

This example shows how to perform a Simulink® Design Verifier™ property proof using a Proof Assumption block.

- Property Proving with an Invalid Property

This example shows how to find an invalid property using Simulink® Design Verifier™ property proving analysis.

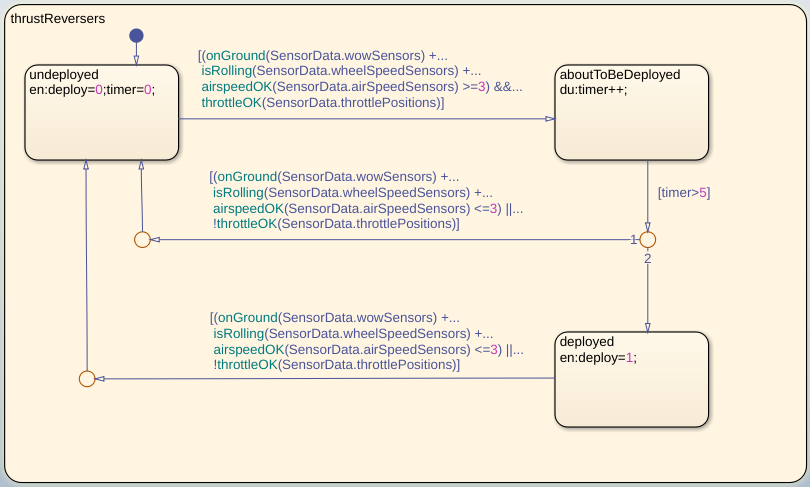

- Debounce Temporal Properties

Model temporal system requirements for property proving and test case generation.

- Power Window Controller Temporal Properties

This example shows how to model temporal system requirements in a power window controller model for property proving and test case generation using Simulink® Design Verifier™ Temporal Operator blocks.

- Prove Properties in Large Models

Use Simulink Design Verifier workflows and best practices for proving properties in large models.

- Verify and Validate a Model and Code

Define requirements, test models and code, check for design errors and standards compliance, and measure test coverage.

- Isolate Verification Logic with Observers

Use Observer blocks to isolate verification logic in a model.