CEI-112G-VSR Transmitter/Receiver IBIS-AMI Model

This example shows how to create IBIS-AMI models for an Optical Internetworking Forum (OIF) CEI-112G-VSR (PAM4) transmitter and receiver for chip-to-module applications. The generated models conform to the IBIS-AMI and OIF-CEI specifications.

The example is divided into three sections:

Set up the target transmitter and receiver IBIS-AMI model architecture for CEI-112G-VSR in the SerDes Designer app

Export the SerDes System to Simulink® for further customization

Generate CEI-112G-VSR Tx/Rx IBIS-AMI Models

Part 1: CEI-112G-VSR Tx/Rx IBIS-AMI Model Architecture Setup

To setup and configure the cei_112g_vsr model in the SerDes Designer app, type the following in the MATLAB® command window :

serdesDesigner('cei_112g_vsr');

The app will open the model. The CEI-112G-VSR compliant transmitter uses a 4-tap feed forward equalizer (FFE) with 2 pre-taps and 1 post-tap. The receiver uses a continuous time linear equalizer (CTLE) with 14 pre-defined configurations, and decision feedback equalizer (DFE) with 4 taps. You can implement these as defined by the OIF specification for CEI-112G-VSR. Many of the values for this system are defined by, or determined from Table 24-14, "COM Parameter Values." The SerDes System is set up as follows:

Configuration Setup

Symbol Time is set to

17.241 ps, representing a symbol rate of 58 Giga-baud and bit rate of 112Gbps due to PAM4 modulationTarget BER is set to

1e-6Modulation is set to

PAM4Samples per Symbol is set to

16Signaling mode is set to

Differential

Transmitter Model Setup

The Tx FFE block is set up for 2 pre-taps, 1 main tap and 1 post-tap and is implemented using a row vector

[0 -0.2 0.7 -0.1]where the main tap is specified by the largest valueThe Tx AnalogOut model is set up so that Voltage is

1.2 V, Rise time is6.869 ps, R (single-ended output resistance) is 50 Ohms, and C (capacitance) is0.217 pF

Channel Model Setup

Channel loss is set to

16 dB(Appendix A, "Recommended Electrical Channel")Differential impedance is kept at the default of

100 OhmsTarget Frequency is set to the Nyquist frequency or

fb/2 = 58GHz/2 = 29GHz

Receiver Model Setup

The Rx AnalogIn model is set up so that R (single-ended input resistance) is

50 Ohmsand C (capacitance) is0 pF(Table 24-14)The Rx CTLE block is set up for 14 configurations using the Specification setting

DC Gain and Peaking Gainand Mode set toadaptThe Rx DFE/CDR block is set up for 4 DFE taps. The minimum values are defined as a row vector

[0 -0.1 -0.1 -0.05]and the maximum values are defined as a row vector[0.4 0.15 0.15 0.1]with mode set toadapt

Plot Statistical Results

You can use plots in SerDes Designer to visualize the results of the CEI-112G-VSR system.

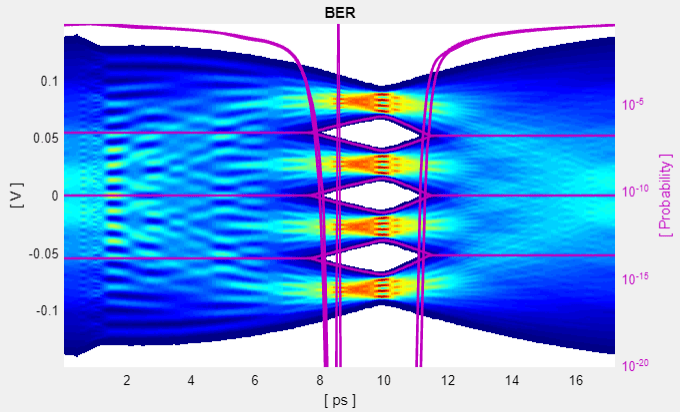

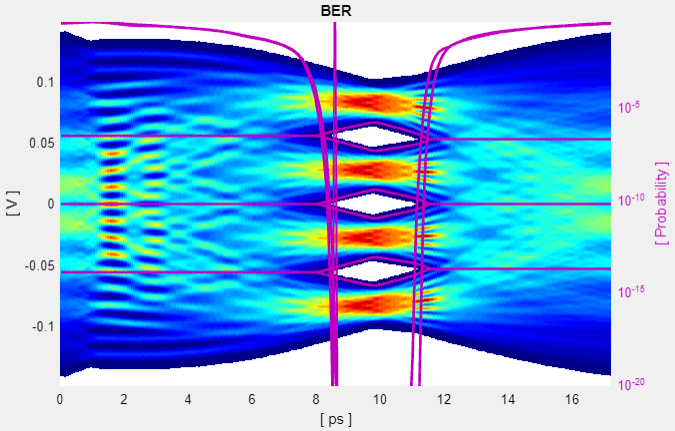

Add the BER plot from Add Plots drop-down list in the toolstrip and observe the results.

Add a Report from Add Plots drop-down list. The report provides data on Eye Heights and Widths, COM, VEC, and post-adaptation tap values for the CTLE and DFE.

In the above report you can see the CTLE adapted to value 10. Try changing the CTLE Mode to fixed and the Configuration Select to 9 and observe that the BER plot changes.

You can also see the values for Eye Heights and Widths change in the Report:

Before continuing, reset the value of Rx CTLE Mode back to adapt as resetting it here will avoid the need to set it again after the model has been exported to Simulink.

Part 2: Export SerDes System to Simulink

Click on the Export button to export the above configuration to Simulink for further customization and generation of the AMI model executables.

CEI-112G-VSR Tx/Rx IBIS-AMI Model Setup in Simulink

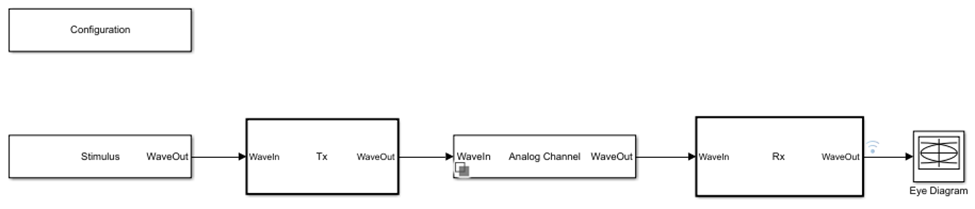

The second part of this example takes the SerDes system exported by the SerDes Designer app and customizes it as required for CEI-112-VSR in Simulink.

Review Simulink Model Setup

The SerDes System exported into Simulink consists of Configuration, Stimulus, Tx, Analog Channel and Rx blocks. All the settings from the SerDes Designer app have been transferred to the Simulink model. Save the model and review each block setup.

Double click the Configuration block to open the Block Parameters dialog box. The parameter values for Symbol time, Samples per symbol, Target BER, Modulation and Signaling are carried over from the SerDes Designer app.

Double click the Stimulus block to open the Block Parameters dialog box. You can set the Waveform Creation Method to Random Symbols or other option to configure the stimulus pattern used during simulation. The settings for this block are not carried over from the SerDes Designer app.

Double click the Tx block to look inside the Tx subsystem. The subsystem has the FFE block carried over from the SerDes Designer app. An Init block is also introduced to model the statistical portion of the AMI model.

Double click the Analog Channel block to open the Block Parameters dialog box. The parameter values for Target frequency, Loss, Impedance and Tx/Rx analog model parameters are carried over from the SerDes Designer app.

Double click on the Rx block to look inside the Rx subsystem. The subsystem has the CTLE and DFECDR blocks carried over from the SerDes Designer app. An Init block is also introduced to model the statistical portion of the AMI model.

Configure Run-Time Parameters with IBIS-AMI Manager

Open the Block Parameter dialog box for the Configuration block and click on the SerDes IBIS-AMI Manager button. In the IBIS tab inside the SerDes IBIS-AMI manager dialog box, the analog model values are converted to standard IBIS parameters that can be used by any industry standard simulator. They also contain run-time parameters that would be used by those EDA tools, and are also used by Simulink for this simulation.

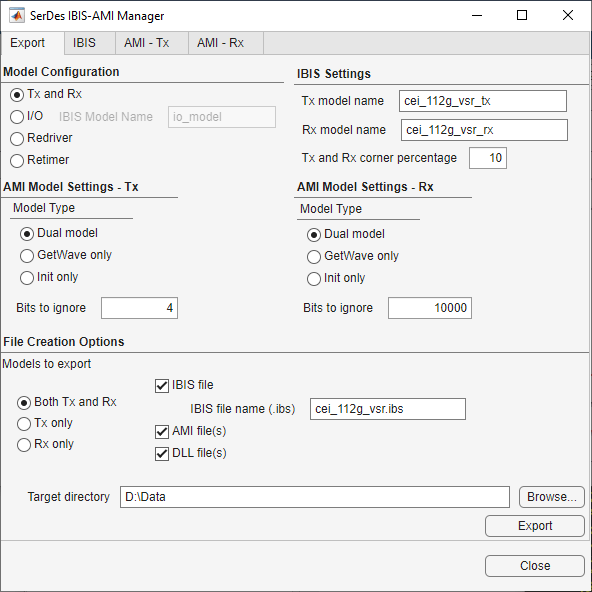

Click on the Export tab and set the following:

AMI Model Settings – Tx:

Bits to ignore: 4

AMI Model Settings – Rx:

Bits to ignore: 20000 (Note: This must be equal or fewer than the symbol count set in Stimulus block in order to display Time Domain Waveforms)

Run the Model

Run the model to simulate the SerDes System.

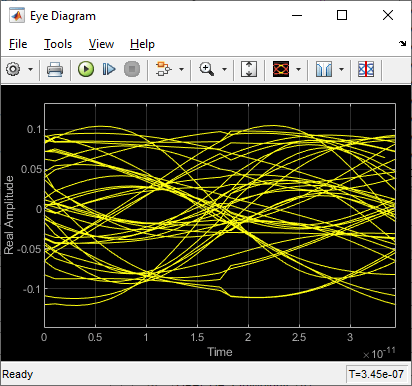

Two plots are generated. The first is a live time domain (GetWave) eye diagram that is updated as the model is running.

A second plot is displayed after simulation is completed that contains views of the statistical (Init) and time domain (GetWave) results, similar to what is available in the SerDes Designer app.

Review Tx FFE Block

Inside the Tx subsystem, double click the FFE block to open the FFE Block Parameters dialog box

Expand the IBIS-AMI parameters to show the list of parameters to be included in the IBIS-AMI model

Verify that Mode and Tap Weights are enabled

Review Rx CTLE Block

Inside the Rx subsystem, double click the CTLE block to open the CTLE Block Parameters dialog box

Gain and Peaking Gain data is carried over from the SerDes Designer app

CTLE Mode is set to Adapt, which means an optimization algorithm built into the CTLE system object selects the optimal CTLE configuration at run time

Review Rx DFECDR Block

Inside the Rx subsystem, double click the DFECDR block to open the DFECDR Block Parameters dialog box

Expand the IBIS-AMI parameters to show the list of parameters to be included in the IBIS-AMI model

Deselect the Phase offset and Reference offset parameters to remove these parameters from the AMI file, effectively hard-coding these parameters to their current values

Verify check boxes are enabled for Mode and Tap Weights

Part 3: Generate CEI-112G-VSR Tx/Rx IBIS-AMI Models

The final part of this example takes the customized Simulink model, modifies the AMI parameters for CEI-112G-VSR, then generates compliant CEI-112G-VSR IBIS-AMI model files.

Open the SerDes IBIS-AMI Manager again. In the Export Tab you can set the model name for the Tx/Rx and the .ibs file. Verify that the Model Configuration is set to "Tx and Rx", that AMI Model Settings for Tx and Rx are set to "Dual Model," and that File Creation Options is set to "Both Tx and Rx." Configure the Tx Ignore Bits to 4, because the FFE has 4 taps. Configure Rx Ignore Bits to 10000 to ensure the DFE has sufficient symbols to converge during adaptation.

In the IBIS tab inside the SerDes IBIS-AMI manager dialog box, the analog model values are converted to standard IBIS parameters that can be used by any industry standard IBIS-AMI simulator. In the AMI-Tx and AMI-Rx tabs in the SerDes IBIS-AMI manager, verify the following are configured to match parameters defined or determined from Table 23-14:

Set Tx FFE Tap Ranges

Highlight TapWeights and click on the Edit button to set:

Verify Tap Weights is set to

[0 0 1 0]to identify setup as [Pre2 Pre1 Main Post1] - the location of the 1 identifies the location of the Main cursor. Also there must be 4 members of this initial vector because this FFE is defined to be 4 UI in length.Set the Min Range to

[0 -0.2 0.65 -0.1]Set the Max Range to

[0.10 0 1.2 0]Click OK to save the changes.

Set Rx CTLE Tap Ranges

Highlight ConfigSelect and click on the Edit button:

Verify the List values are set to

[0 1 2 3 4 5 6 7 8 9 10 11 12 13]Set the List_Tip values to describe each settings

["-0dB" "-1dB" "-2dB" "-3dB" "-4dB" "-5dB" "-6dB" "-7dB" "-8dB" "-9dB" "-10dB" "-11dB" "-12dB" "-13dB"]Click OK to save the changes.

Set Rx DFECDR Tap Ranges

Highlight TapWeight and click the Edit button to set the following:

Verify Tap Weights is set to

[0.4 0 0 0]Note: there must be 4 members of this initial vector because this DFE is defined to be 4 UI in length.Set the Min Range to

[0 -0.1 -0.1 -0.05]Set the Max Range to

[0.4 0.15 0.15 0.1]Click OK to save the changes.

Export Models

Select the Export tab in the SerDes IBIS-AMI manager dialog box.

Update the Tx model name to

cei_112g_vsr_txUpdate the Rx model name to

cei_112g_vsr_rxNote that the Tx and Rx corner percentage is set to 10%. This will scale the min/max analog model corner values by +/-10%.

Verify that Dual model is selected for both the Tx and the Rx. This will create model executables that support both statistical (Init) and time domain (GetWave) analysis.

Set the Tx model Bits to ignore value to 4 since there are four taps in the Tx FFE.

Set the Rx model Bits to ignore value to 20000 (20000 UI will allow sufficient time for the Rx DFE taps to converge and adapt during time domain simulations).

Verify that Both Tx and Rx are set to Export and that all files have been selected to be generated (IBIS file, AMI files and DLL files).

Set the IBIS file name to be

cei_112g_vsr.ibsPress the Export button to generate models in your Target directory.

Test Generated IBIS-AMI Models

The CEI-112G-VSR transmitter and receiver IBIS-AMI models are now complete and ready to be operated in any industry standard AMI model simulator.

References

[1] IBIS (I/O Buffer Information Specification), Version 7.0, https://ibis.org/ver7.0/ver7_0.pdf.

[2] OIF Forum, CEI-112G-VSR, Contribution Number oif2017.346.22-1.pdf, https://www.oiforum.com.

[3]

See Also

FFE | CTLE | DFECDR | SerDes Designer

Topics

- Managing AMI Parameters

- CEI 112G-VSR Compliance Kit (Signal Integrity Toolbox)