Generate HDL Code from MATLAB Code by Using Native Floating-Point and Vendor Floating-Point Library IP

This example shows how to use the floating-point IP provided by the AMD® Vivado synthesis tool to generate HDL code that incorporates HDL Coder™ native floating-point (NFP) and AMD® floating-point IP from MATLAB® code. In this example, you use the MATLAB Workflow Advisor and the command-line interface to generate the HDL code, HDL test bench, and HDL simulation script files.

Set Up Tool Path

Set up the third-party synthesis tool path. This example uses the AMD® Vivado® synthesis tool. Use the hdlsetuptoolpath function to specify the path to the installed AMD Vivado executable:

hdlsetuptoolpath("ToolName","Xilinx Vivado","ToolPath", "C:\Xilinx\Vivado\2024.1\bin\vivado.bat");

This example uses the Siemens® ModelSim simulation tool, which is the supported tool when you use the vendor floating-point library. Set up the path to the simulation tool:

setenv("PATH", ["c:\Program Files\ModelSim\questasim-2023.2\win64\vsim.exe;", getenv('PATH')]);

Generate HDL Code Using Workflow Advisor

To generate HDL code by using the MATLAB Workflow Advisor, create an HDL code generation project, specify the function and test bench files, specify the fixed-point conversion parameters, define the code generation target, configure the floating-point options, and generate an HDL test bench.

Create HDL Code Generation Project

To create an HDL Code Generation project, in the Apps tab, click HDL Coder. Specify your project name and location, and click OK. In the HDL Code Generation window:

Set MATLAB Function to

singleOps.m.Set MATLAB Test Bench to

singleOps_tb.m.In the MATLAB Function section, to automatically define the input types based on the signal data types specified in the test bench, click Autodefine types > Run. Next, review the input types, and click Use These Types.

Click Workflow Advisor.

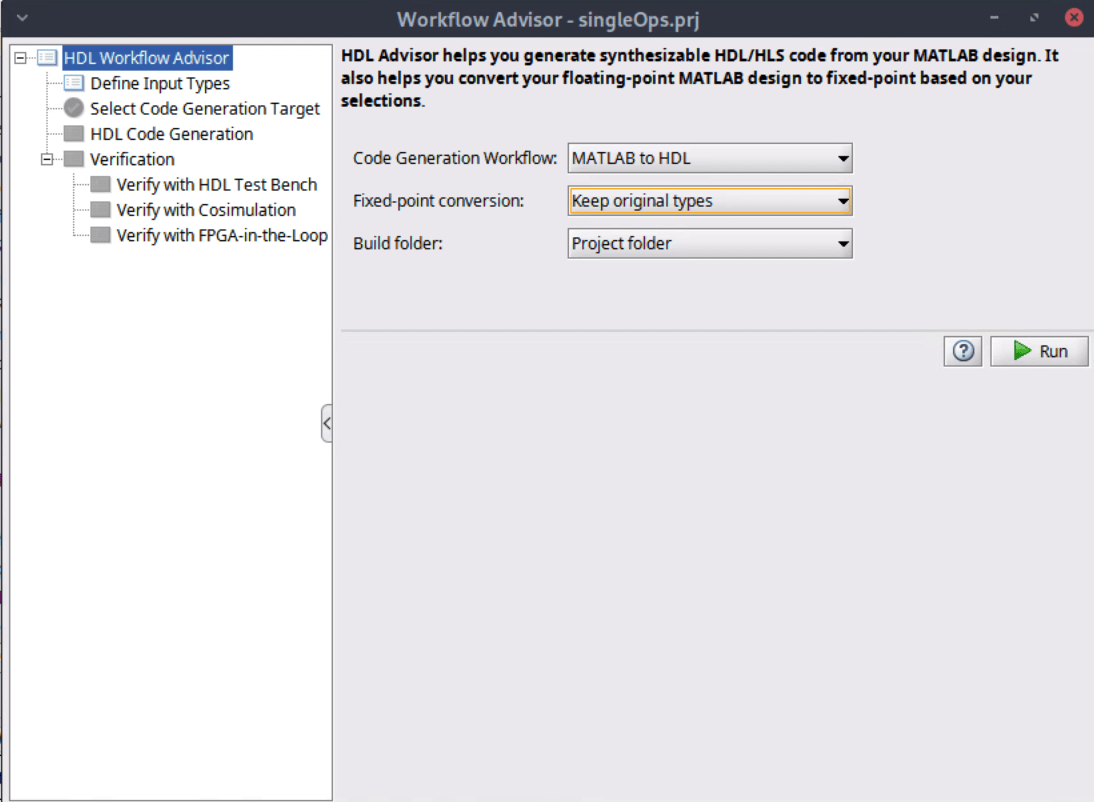

To generate HDL code that uses floating-point libraries, set the Fixed-point conversion parameter to Keep original types.

Define Code Generation Target

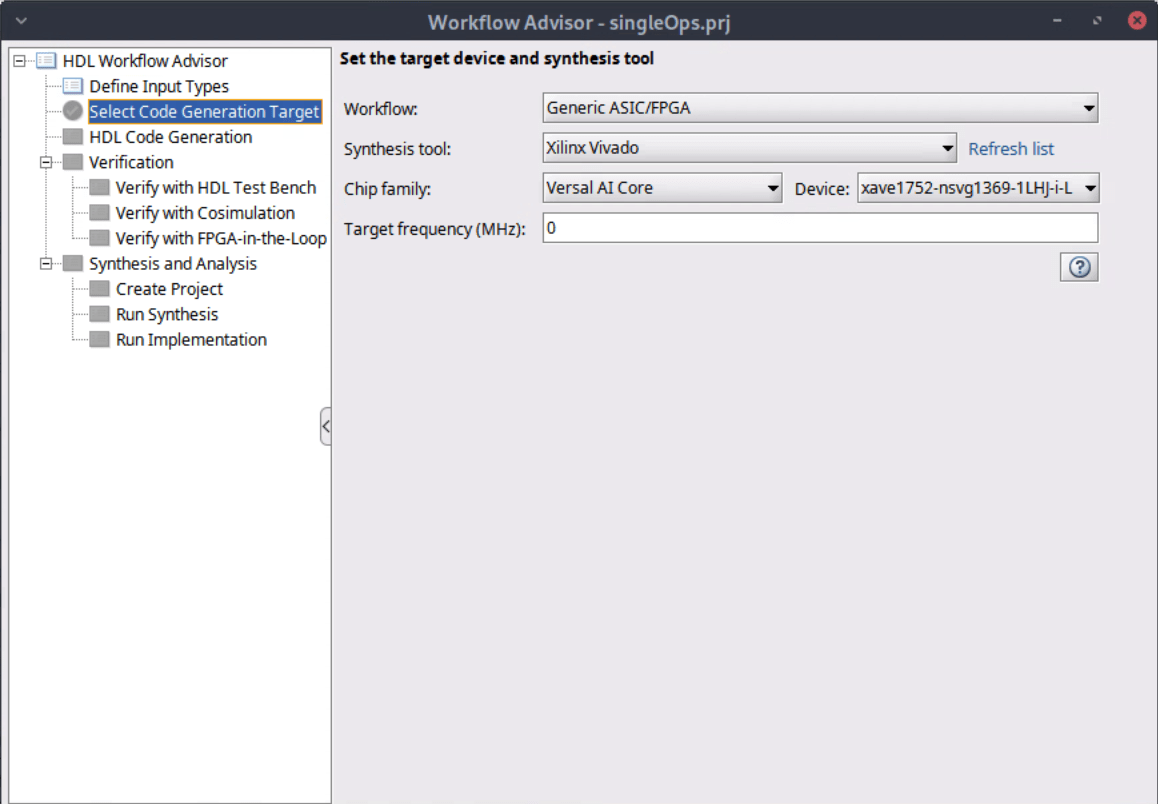

In the Select Code Generation Target task, set the synthesis tool and FPGA device information. For this example, set:

Synthesis tool to

Xilinx VivadoChip family to

Versal AI Core

Configure Floating-Point Libraries

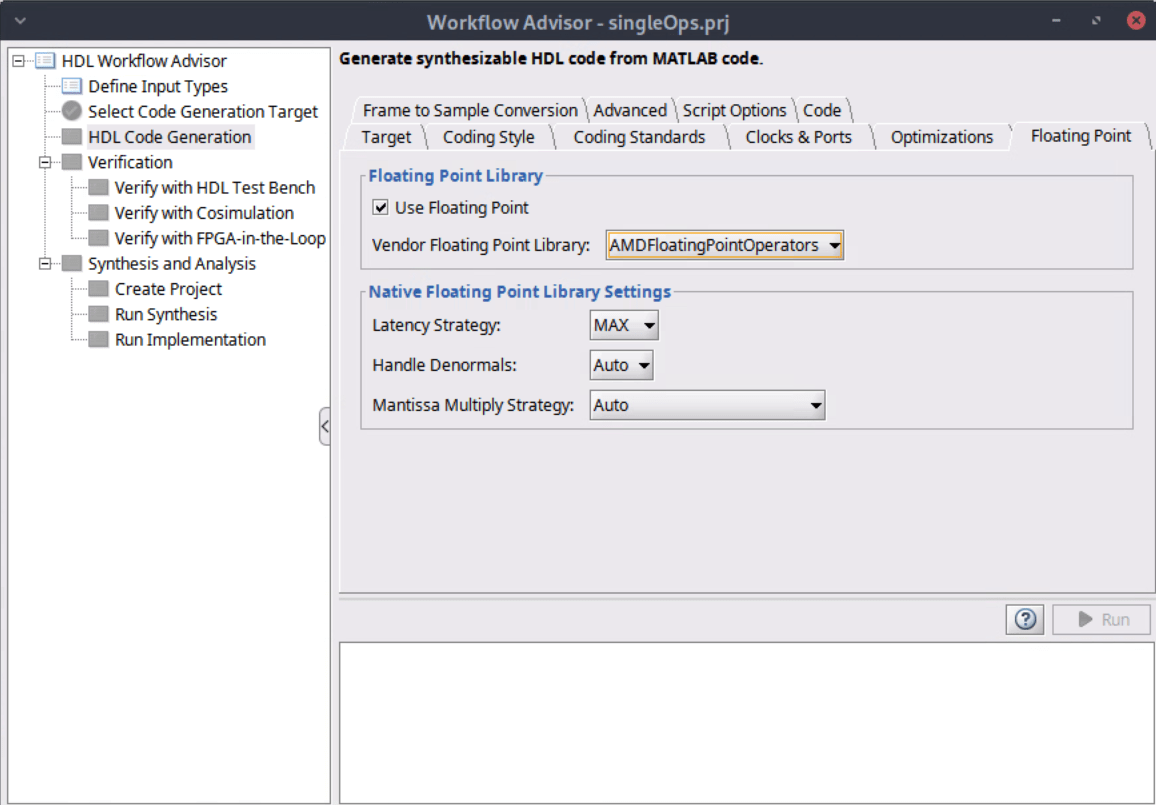

HDL Coder supports the generation of HDL code using the AMD® floating-point library, (AMDFloatingPointOperators), or the Intel® FPGA floating-point IP library, (AlteraFPFunctions), together with the HDL Coder native floating-point library. For other synthesis tool settings, you can use the native floating-point library to generate HDL code.

in the HDL Code Generation task, in the Floating Point tab, enable Use Floating Point and then set Vendor Floating Point Library to AMDFloatingPointOperators.

If you customize the native floating-point library settings in the Floating Point tab, you must generate HDL code from the command-line interface.

Set Up the HDL Test Bench

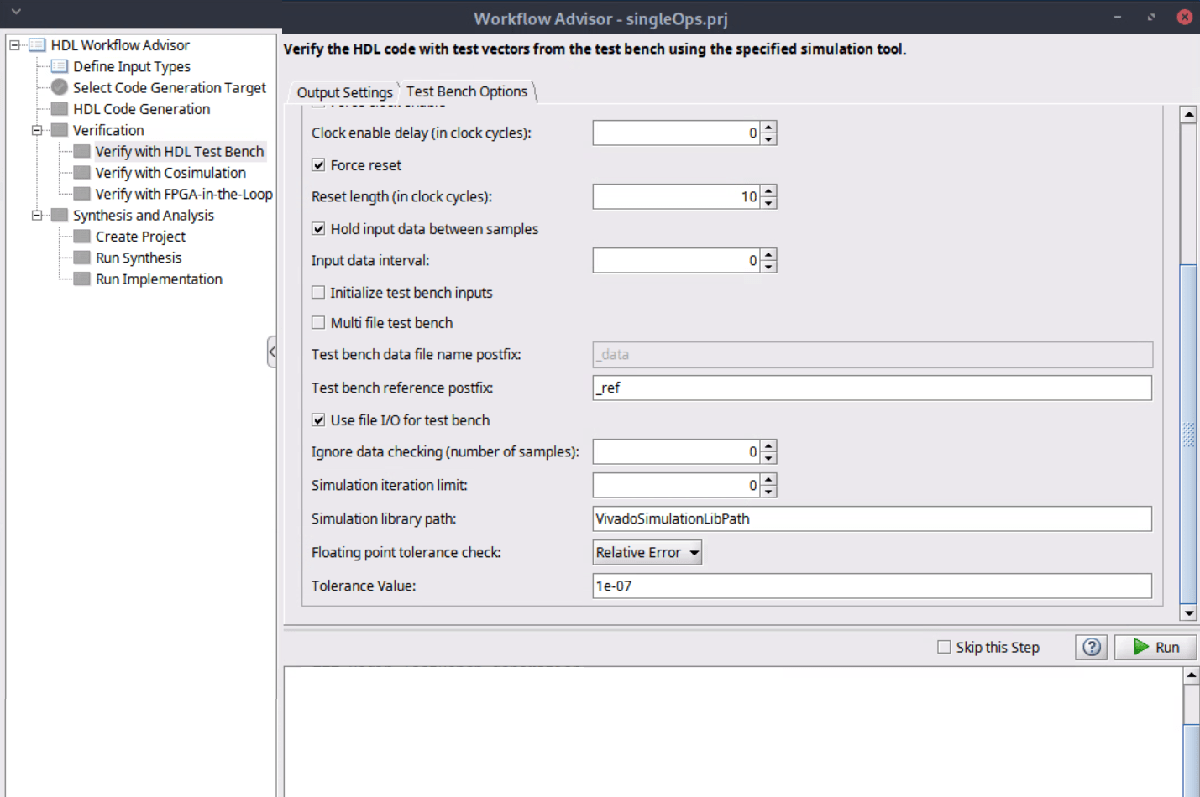

To simulate the generated HDL code and HDL test bench with the AMD floating-point library, click the Verify with HDL Test Bench task. In the Test Bench Options tab, set the Reset length (in clock cycles) parameter to 10. HDL Coder does not support using the Vivado Simulator as the HDL simulation tool when you use the AMD floating-point library.

Set the Simulation library path parameter to the path to your compiled Vivado simulation libraries for ModelSim.

To generate the HDL test bench files, in the Output Settings tab, enable Generate test bench.

You can also verify the generated files by selecting the Simulate generated test bench option and setting the Simulation tool to ModelSim. If the simulation passes, the Workflow Advisor displays Simulation Successful. You must add the ModelSim path to set the Simulation tool to ModelSim. If the ModelSim option is not available, add the ModelSim path to the MATLAB search path, and click Refresh list.

Generate HDL Code Using the Command-Line Interface

To generate HDL code from the command-line interface, create an HDL Coder configuration object, configure the object, run the code generation command, and then compile and simulate the model using ModelSim.

Create HDL Coder Configuration Object

To generate HDL code, you need the MATLAB design file singleOps.m, and the test bench file, singleOps_tb.m.

Create a HDL Coder configuration object and set the DesignFunctionName and TestBenchName properties.

hdlcfg = coder.config("hdl"); hdlcfg.DesignFunctionName = "singleOps"; hdlcfg.TestBenchName = "singleOps_tb";

Configure HDL Coder Configuration Object

hdlcfg.SynthesisTool = "Xilinx Vivado"; hdlcfg.SynthesisToolChipFamily = "Versal AI Core"; hdlcfg.SynthesisToolDeviceName = "xcvc1802-viva1596-1LHP-i-L";

Set the path to your compiled Vivado simulation library. By default, the compiled simulation library is located at 'C:\HDLTools\Vivado\ModelSim_SimLibs\2023.2\'. Update this path to the location of your compiled library.

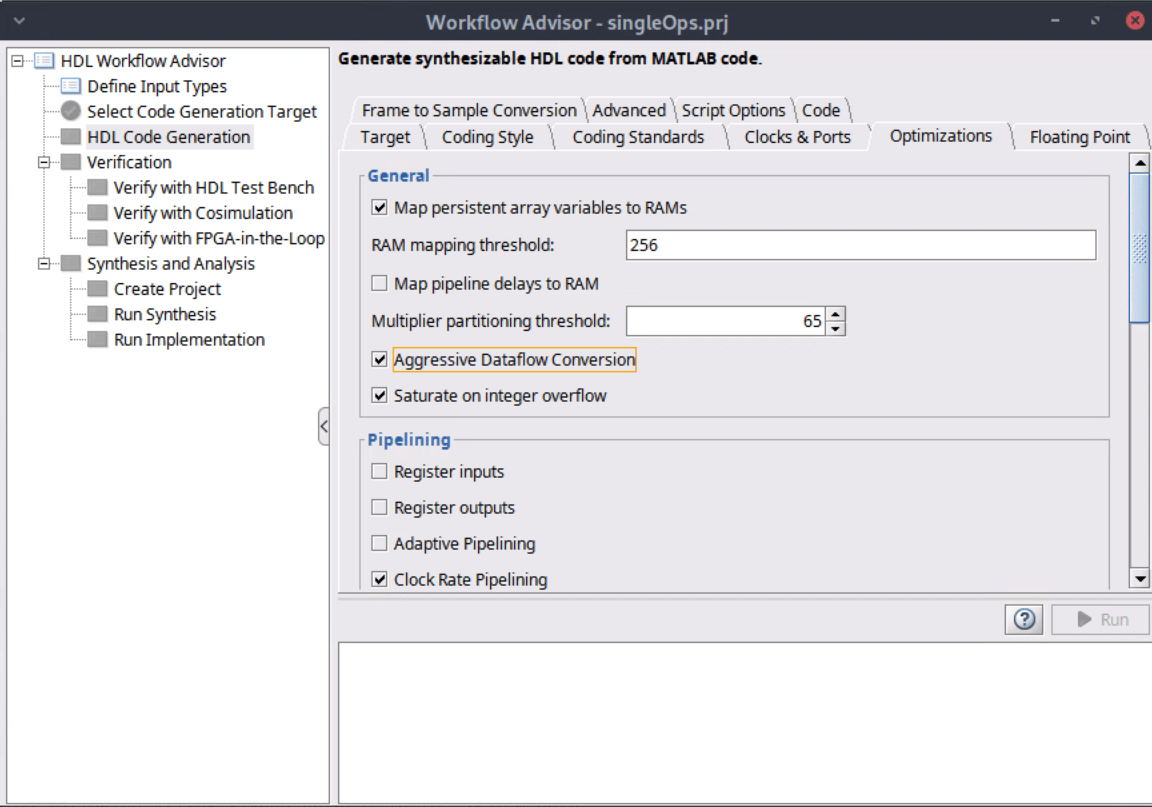

hdlcfg.SimulationLibPath = "C:\HDLTools\Vivado\ModelSim_SimLibs\2023.2\";In the MATLAB design, the exponential and divide function are not supported by the AMD floating-point IP library. To use floating-point for these functions, enable AggressiveDataflowConversion to map the exponential and divide function to the HDL Coder native floating-point library.

hdlcfg.AggressiveDataflowConversion = true;

The AMD floating-point IP requires the reset signal be low for at least 10 cycles to reset the floating point IP. Set the ResetLength property to 10.

hdlcfg.ResetLength = 10;

Create a floating-point target configuration object for mixed native floating-point and AMD floating-point libraries by using the createFloatingPointTargetConfig function and setting the VendorFloatingPointLibrary name-value argument to AMDFloatingPointOperators. For more information on creating a floating-point target configuration object, see createFloatingPointTargetConfig.

fpconfig = hdlcoder.createFloatingPointTargetConfig(VendorFloatingPointLibrary = 'AMDFLOATINGPOINTOPERATORS'); fpconfig.VendorLibrarySettings.DSPSliceUsage = 'Primitive'; fpconfig.VendorIPConfig.customize('Mul_Primitive', 'Single', 'Latency', 2); fpconfig.LibrarySettings.LatencyStrategy = "Min"; hdlcfg.FloatingPointTargetConfiguration = fpconfig;

To generate a test bench that runs a ModelSim simulation, set the GenerateHDLTestBench property to true.

hdlcfg.GenerateHDLTestBench = true;

Run Code Generation

Use the codegen command to generate the HDL code and test bench. The exponential IP requires 16 cycles and the divide IP requires 17 cycles because the native floating-point library uses the minimum latency strategy. The addition IP uses the maximum latency value of 2 cycles.

codegen -config hdlcfg

### Begin MATLAB to HDL Code Generation...

### Working on DUT: singleOps.

### Using TestBench: singleOps_tb.

### Using D:\share\apps\HDLTools\Vivado\2024.1-mw-0\Win\Vivado\2024.1\bin\vivado for the selected floating point IP library.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 35 cycles.

### Generating AMD(R) floating point block: amdfp_add_single for latency of 2.

### Found an existing generated file in a previous session: (C:\ExampleManager83beb2\user.12112025\hdlcoder-ex28930989\codegen\singleOps\hdlsrc\Xilinx\Versal_AI_Core\xcvc1802-viva1596-1LHP-i-L\L2\amdfp_add_single\amdfp_add_single.vhd). Reusing the generated file.

### Done.

### Begin VHDL Code Generation

### Working on singleOps/amdfp_add_single_block as amdfp_add_single_block.vhd.

### Working on singleOps/nfp_div_single as nfp_div_single.vhd.

### Working on singleOps/nfp_exp_single as nfp_exp_single.vhd.

### Working on singleOps/nfp_uminus_single as nfp_uminus_single.vhd.

### Working on singleOps as singleOps.vhd.

### Generating package file singleOps_pkg.vhd.

### Generating Resource Utilization Report resource_report.html.

### Generating Optimization report

### To rerun codegen evaluate the following commands...

---------------------

cgi = load('C:\ExampleManager83beb2\user.12112025\hdlcoder-ex28930989\codegen\singleOps\hdlsrc\codegen_info.mat');

inVals = cgi.CodeGenInfo.inVals;

cfg = cgi.CodeGenInfo.codegenSettings;

codegen -config cfg -args inVals -report

---------------------

### Begin TestBench generation.

Code generation successful.

### Accounting for latency of output port : 35 cycles.

### Collecting data...

### Begin HDL test bench file generation with logged samples

### Generating test bench data file: a.dat.

### Generating test bench data file: sigmoid_out_expected.dat.

### Working on singleOps_tb as singleOps_tb.vhd.

### Generating package file singleOps_tb_pkg.vhd.

### Generating HDL Conformance Report singleOps_hdl_conformance_report.html.

### HDL Conformance check complete with 0 errors, 0 warnings, and 0 messages.

### Code generation successful: View report

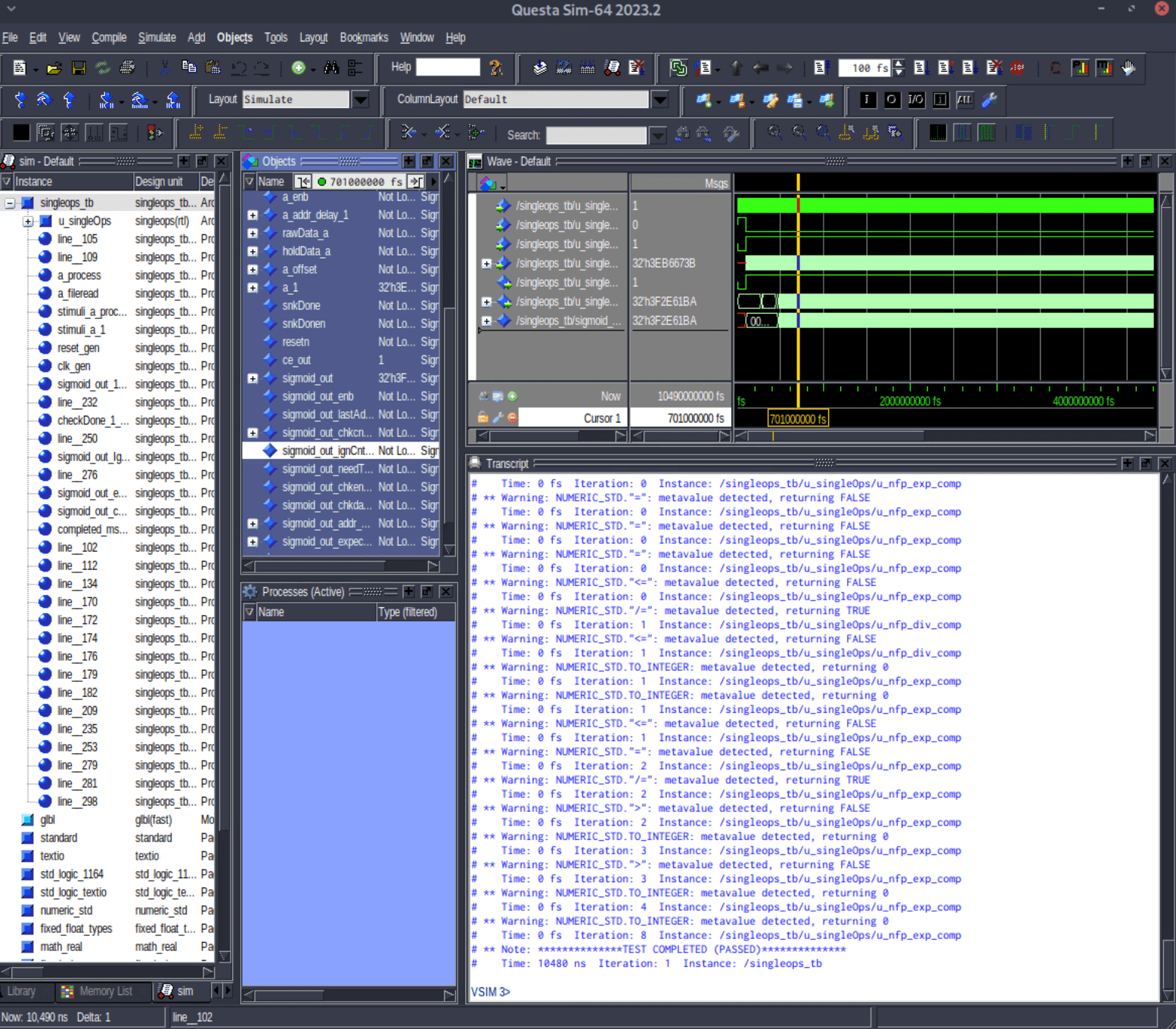

Verify the Generated HDL Code by Using Generated ModelSim Simulation Scripts

The code generation process generates these ModelSim DO files to simulate your design in the Siemens® ModelSim® software. HDL Coder generates a simulation script for the ModelSim simulation tool when you use the vendor floating-point library. The code generation process generates these ModelSim DO files in the codegen/singleOps/hdlsrc folder.

singleOps_tb_compile.dofile compiles the generated HDL files and loads the entity to be tested (singleOps.vhd) and its test bench code (singleOps_tb.vhd).singleOps_tb_sim.doinitializes the simulator, sets up the wave window signal displays, and runs a simulation.

To verify the simulation results, open the ModelSim software and navigate to the codegen/singleOps/hdlsrc folder.

Use the generated compilation script to compile and load the design and test bench code.

QuestaSim>do HDL_DUT_tb_compile.do

2. Use the generated simulation script to execute the simulation.

QuestaSim>do HDL_DUT_tb_sim.do

After the ModelSim simulation completes, the message at the end of the log window indicates that the test passes.

See Also

createFloatingPointTargetConfig