Generate Code for AMD Blocks by Using AMD Vitis Model Composer

In this example, you generate integrated HDL code for the models that contain AMD® blocks by using Vitis® Model Composer and HDL Coder™. AMD Vitis Model Composer is a model-based design tool that uses the MATLAB® environment to design a system that contains various performance-optimized AMD HDL blocks. You can use this tool to iteratively explore designs, validate system-level functionality, or implement complex algorithms on AMD devices.

Vitis Model Composer has the functionalities of AMD System Generator for DSP. For more information, see Vitis Model Composer on the AMD website.

Create a Model Using AMD Blocks

This example uses AMD Vitis Model Composer to create a model that contains both Simulink and AMD blocks.

Requirements

For this example, you require:

AMD Vitis Model Composer 2024.1 or later.

AMD Vivado® Design Suite.

A version of MATLAB that is compatible with Vitis Model Composer.

Windows® operating system.

To learn more about the system requirements for the Vitis Model Composer, see System Requirements for Vitis Model Composer.

To design a Simulink® model with AMD blocks:

Open AMD Vitis Model Composer. Vitis Model Composer opens a new MATLAB session where you can design your model.

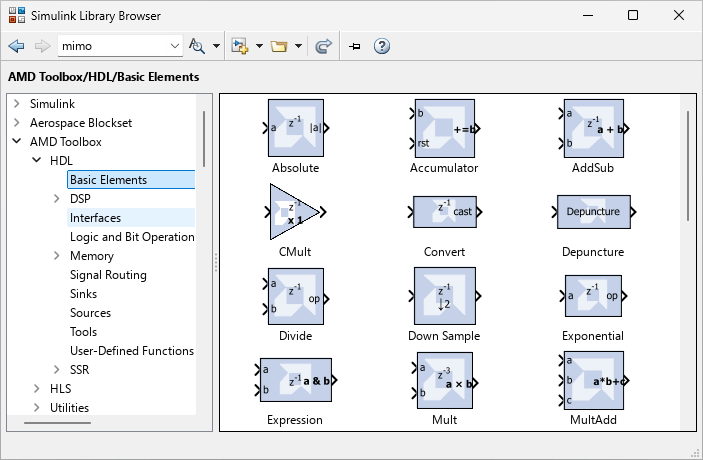

In Simulink, create a model that contains Simulink and AMD blocks. The AMD Toolbox library contains AMD HDL blocks.

Group the AMD blocks into a subsystem. The subsystem can have multiple hierarchy of subsystems.

Connect the input and output ports of the AMD blocks subsystem to Gateway In and Gateway Out blocks.

Add a Vitis Model Composer Hub block. Configure the properties for the Vitis Model Composer Hub block.

Enclose the subsystem that contains the Vitis Model Composer Hub block and other AMD blocks into another subsystem. Set the Architecture HDL block property of the subsystem to

Module.Configure the HDL Code Generation configuration parameter for model or top-level subsystem.

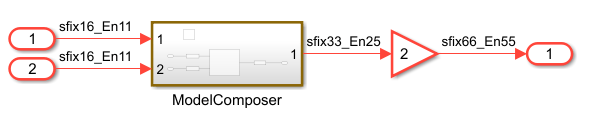

The hdlcoderModelComposer model uses both Simulink and AMD blocks.

Open the hdlcoderModelComposer model.

load_system('hdlcoderModelComposer') open_system('hdlcoderModelComposer/DUT/ModelComposer')

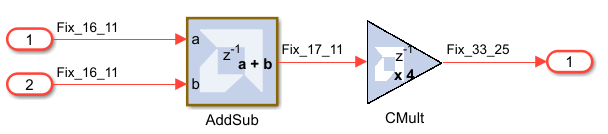

In the ModelComposer subsystem, the input and output ports of AMD_HDL subsystem connect to Gateway IN and Gateway Out blocks. The Vitis Model Composer Hub block is at the top of the subsystem hierarchy. The AMD_HDL subsystem contains the AMD Toolbox AddSub and CMult blocks.

open_system('hdlcoderModelComposer/DUT/ModelComposer/AMD_HDL')

To set the properties of Vitis Model Composer Hub block, double-click on the block.

In the Hardware Selection section, set the Select Hardware to your target hardware.

In the Code Generation section, in the Settings tab, set the target language, clock settings and other settings.

In the Code Generation section, in the Export tab, set Export Type to

HDL Netlistand clear Generate testbench.

Generate HDL Code

To generate the VHDL code for the DUT subsystem, run:

makehdl('hdlcoderModelComposer/DUT',TargetLanguage="VHDL")

HDL Coder generates HDL code from the Simulink blocks and uses AMD Vitis Model Composer to generate HDL code for the AMD blocks. You can also generate test bench for your model and verify the system functionality.

Limitations

When you generate HDL code for model that has AMD blocks, follow these guidelines:

Vitis Model Composer does not support SystemVerilog code generation for AMD blocks.

The subsystem that contains the Vitis Model Composer Hub block cannot be a design-under-test (DUT) subsystem for HDL code generation.

Enable the Propagate data type to output block property of Gateway Out blocks to propagate Vitis Model Composer data types to an approximate Simulink data type.

Gateway In blocks can only do trivial data type conversion. For example, a Gateway In block can convert between the

sfix8_en6andFix_8_6data types, but cannot convert data signedness, word length, or fraction length.HDL Coder does not generate code for Simulink blocks that are inside the Vitis Model Composer subsystem.

Use the same target language for the Vitis Model Composer Hub block and HDL code generation. If the code generation settings for the Vitis Model Composer Hub block and HDL Coder are different, HDL Coder uses the code generation settings for the Simulink model.

The Vitis Model Composer subsystem supports only the ConstrainedOutputPipeline, InputPipeline, and OutputPipeline HDL block properties.

See Also

Create an Altera DSP Builder Subsystem