Simulate and Generate HDL Code for Unit Delay Resettable Synchronous Block

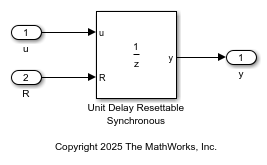

This example shows how to implement the Unit Delay Resettable Synchronous block in a Simulink® model. The Unit Delay Resettable Synchronous block delays the input signal by one sample period when external reset signal is 0. When the reset signal is 1, the state and the output signal takes the value of Initial condition parameter after one sample period. You can generate HDL code for the model.

Load and Open Model

Load and open the UnitDelayResettableSynchronousModel model. The DUT subsystem contains a Unit Delay Resettable Synchronous block, with the Initial condition parameter is set to 0.

load_system("UnitDelayResettableSynchronousModel"); open_system("UnitDelayResettableSynchronousModel/DUT");

Simulate Design

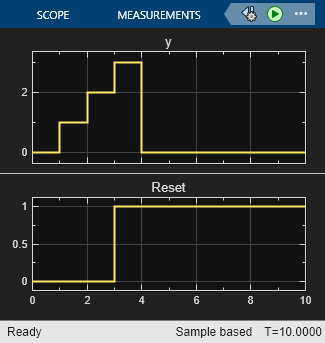

Simulate the UnitDelayResettableSynchronousModel model. The block returns the output signal delayed by one sample period when the external reset signal is 0. When the external reset signal is 1, the output signal is changed to 0 after one sample period.

sim('UnitDelayResettableSynchronousModel');

Generate HDL Code

You can generate the HDL code for a model by using HDL Coder™. Generate the HDL code for DUT subsystem using the makehdl function.

makehdl("UnitDelayResettableSynchronousModel/DUT")