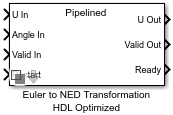

Euler to NED Transformation HDL Optimized

Computes Euler to North-East-Down transformation using pipelined or burst architecture and generates optimized HDL code

Since R2022b

Libraries:

Fixed-Point Designer HDL Support /

Coordinate Transformations

Description

The Euler to NED Transformation HDL Optimized block provides two architectures that implement Euler to North-East-Down (NED) transformation using a CORDIC rotation kernel for FPGA and ASIC applications.

You can select an architecture that optimizes for either throughput or area.

Pipelined— Use this architecture for high-throughput applications.Burst— Use this architecture for a minimum resource implementation.

The Euler to NED Transformation HDL Optimized block provides hardware-friendly control signals.

Ports

Input

Input array, specified as a 3-by-1 vector.

Fixed-point inputs must use binary-point scaling.

Example:

UIn = [0;0;1]

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Complex Number Support: Yes

Angles to rotate by, specified as a 3-by-1 real-valued vector containing the angles phi, theta, and psi in radians.

Example:

AngleIn = [phi;theta;psi]

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Whether input is valid, specified as a Boolean scalar. This control signal

indicates when the data from the U In and Angle

In input ports are valid. When this value is 1

(true), the block captures the values at the input ports

U In and Angle In. When this value is

0 (false), the block ignores the input

samples.

Data Types: Boolean

Whether to clear internal states, specified as a Boolean scalar. When this value

is 1 (true), the block stops the current calculation and clears all

internal states. When this value is 0 (false) and the

Valid In value is 1 (true), the block begins

a new subframe.

Data Types: Boolean

Output

Rotated array, returned as a 3-by-1 vector.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Whether the output data is valid, returned as a Boolean scalar. When the value of

this control signal is 1 (true), the block has

successfully computed the output U Out. When this value is

0 (false), the output data is not

valid.

Data Types: Boolean

Whether the block is ready for input, returned as a Boolean scalar. This control

signal indicates when the block is ready for new input data. When this value is 1

(true) and Valid In value is 1

(true), the block accepts input data in the next time step. When

this value is 0 (false), the block ignores input data in the next

time step.

Data Types: Boolean

Parameters

This parameter specifies the type of architecture.

Pipelined— Select this value to specify low-latency architecture.Burst— Select this value to specify minimum resource architecture.

Programmatic Use

Block Parameter:

Architecture |

| Type: character vector |

Values:

'Pipelined' | 'Burst' |

Default:

'Pipelined' |

Algorithms

The Euler to North-East-Down (NED) transformation is carried out by the successive application of these three rotation matrices.

Multiplying these matrices together gives the total transformation.

You can transform between two frames related by the angles ϕ, θ

, and ψ by multiplying a vector in an initial frame by the matrix above.

CORDIC is an acronym for COordinate Rotation Digital Computer. The Givens rotation-based CORDIC algorithm is one of the most hardware-efficient algorithms available because it requires only iterative shift-add operations. It is an iterative algorithm that approximates the solution by converging toward the ideal point. Using CORDIC, you can calculate various functions such as sine and cosine.

To use CORDIC to solve the Euler-NED transformation, CORDIC Givens rotations are applied sequentially in the appropriate subspaces of the initial space. First, rotate by ϕ in the yz-plane, then rotate by -θ in the xz-plane, then rotate by ψ in the xy-plane.

This resource and performance data is the synthesis result from the generated HDL targeted to a Virtex®-7.

| Algorithm | Flip Flops | LUT | LUTRAM | DSPs |

|---|---|---|---|---|

| Pipelined CORDIC (sfix14En10) | 3141 | 86 | 3973 | 0 |

| Resource Shared CORDIC (sfix14En10) | 337 | 659 | 0 | 0 |

| Algorithm | Clock Frequency (MHz) | Latency (Cycles) | Latency (ns) |

|---|---|---|---|

| Pipelined CORDIC (sfix14En10) | 347 | 63 | 181 |

| Resource Shared CORDIC (sfix14En10) | 347 | 57 | 164 |

Extended Capabilities

Supports fixed-point data types only. Fixed-point data types must use binary-point scaling.

Generated C/C++ code will have timing of the HDL block.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| General | |

|---|---|

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

Supports fixed-point data types only. Fixed-point data types must use binary-point scaling.

Fixed-Point Conversion

Design and simulate fixed-point systems using Fixed-Point Designer™.

Version History

Introduced in R2022b

See Also

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)