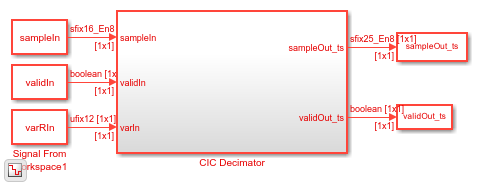

CIC Decimator

Decimate signal using CIC filter

Libraries:

DSP HDL Toolbox /

Filtering

Description

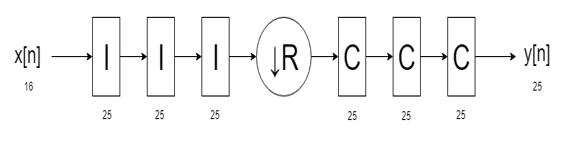

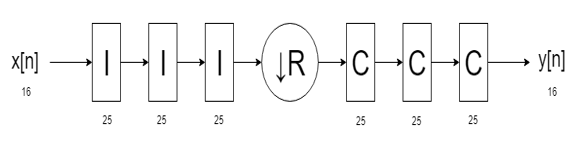

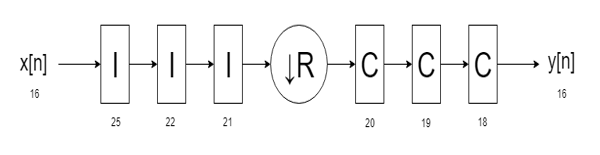

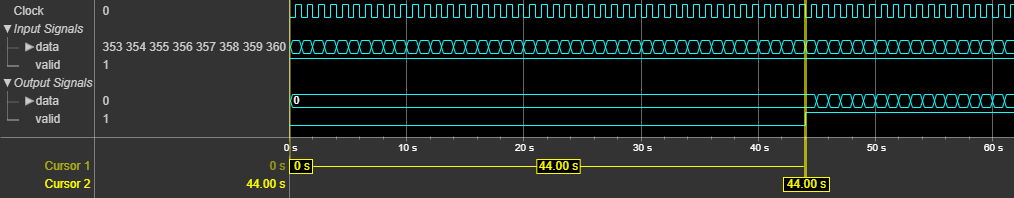

The CIC Decimator block decimates an input signal by using a cascaded integrator-comb (CIC) decimation filter. CIC decimation filters are a class of linear phase finite impulse response (FIR) filters consisting of a comb part and an integrator part. The CIC decimation filter structure consists of N sections of cascaded integrators, a rate change factor of R, and N sections of cascaded comb filters. For more information about CIC decimation filters, see Algorithms.

The block supports these combinations of input and output data.

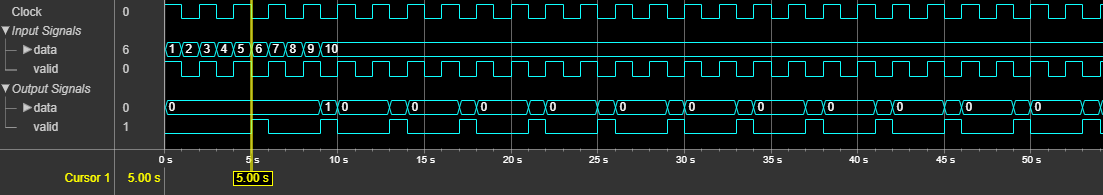

Scalar input and scalar output — Support for fixed and variable decimation rates

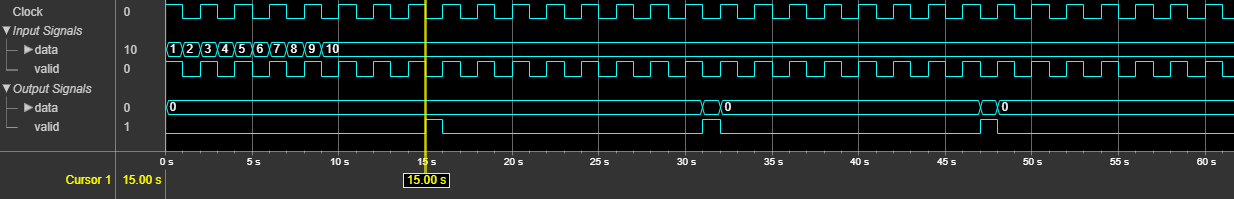

Vector input and scalar output — Support for fixed decimation rates only

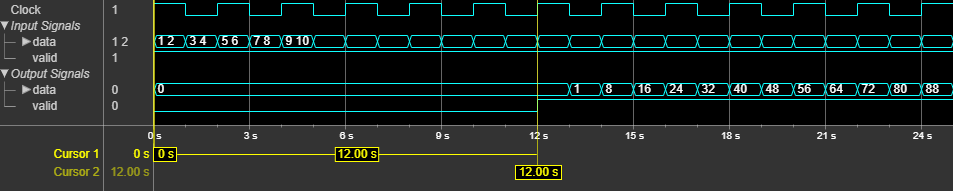

Vector input and vector output — Support for fixed decimation rates only

The block provides an architecture suitable for HDL code generation and hardware deployment.

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a Simulink® model, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the Simulink block.

Examples

Ports

Input

Output

Parameters

Tips

Reset Behavior

By default, the CIC Decimator block connects the generated HDL global reset to only the control path registers. The two reset parameters, Enable reset input port and Use HDL global reset, connect a reset signal to the data path registers. Because of the additional routing and loading on the reset signal, resetting data path registers can reduce synthesis performance.

The Enable reset input port parameter enables the reset port on the block. The reset signal implements a local synchronous reset of the data path registers. For optimal use of FPGA resources, this option does not connect the reset signal to registers targeted to the DSP blocks of the FPGA.

The Use HDL global reset parameter connects the generated HDL global reset signal to the data path registers. This parameter does not change the appearance of the block or modify simulation behavior in Simulink. The generated HDL global reset can be synchronous or asynchronous depending on the HDL Code Generation > Global Settings > Reset type parameter in the model Configuration Parameters. Depending on your device, using the global reset might move registers out of the DSP blocks and increase resource use.

When you select the Enable reset input port and Use HDL global reset parameters together, the global and local reset signals clear the control and data path registers.

Reset Considerations for Generated Test Benches

FPGA-in-the-loop (FIL) initialization provides a global reset but does not automatically provide a local reset. With the default reset parameters, the data path registers that are not reset can result in FIL mismatches if you run the FIL model more than once without resetting the board. Select Use HDL global reset to reset the data path registers automatically, or select Enable reset input port and assert the local reset in your model so the reset signal becomes part of the Simulink FIL test bench.

The generated HDL test bench provides a global reset but does not automatically provide a local reset. With the default reset parameters and the default register reset Configuration Parameters, the generated HDL code includes an initial simulation value for the data path registers. However, if you are concerned about

X-propagation in your design, you can set the HDL Code Generation > Global Settings > Coding style > No-reset registers initialization parameter in Configuration Parameters toDo not initialize. In this case, with the default block reset parameters, the data path registers that are not reset can causeX-propagation on the data path at the start of HDL simulation. Select Use HDL global reset to reset the data path registers automatically, or select Enable reset input port and assert the local reset in your model so the reset signal becomes part of the generated HDL test bench.

Algorithms

References

[1] Hogenauer, E. “An Economical Class of Digital Filters for Decimation and Interpolation.” IEEE Transactions on Acoustics, Speech, and Signal Processing 29, no. 2 (April 1981): 155–62. https://doi.org/10.1109/TASSP.1981.1163535.