PIL Simulation

A processor-in-the-loop (PIL) simulation cross-compiles source code on your development computer, and then downloads and runs the object code on the processor in the hardware board. With SoC Blockset™ and C2000™ Microcontroller Blockset features, you can run parts of your model on the supported Texas Instruments® hardware board to get direct measurements of algorithm and task execution time from the processor. The measurements can be used to improve the quality of the simulations.

Two types of PIL simulations can be used with the SoC Blockset models and the supported Texas Instruments hardware board: block level simulation and top-model simulation. These sections describe the two types of PIL simulations available when using SoC Blockset models. For general information on PIL simulations, see SIL and PIL Simulations (Embedded Coder).

Note

PIL simulation with C2000 Microcontroller Blockset is only supported using the SCI_A communication

channel.

Block-Level PIL Simulation

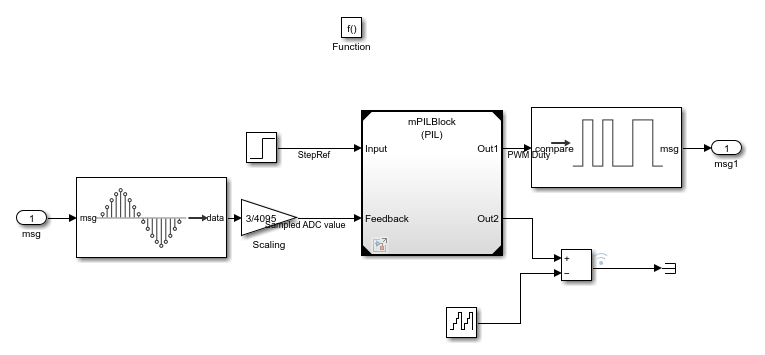

Open a C2000 Microcontroller Blockset model, such as the closed-loop control system shown in this figure.

Open the Control Algorithm reference model that represents CPU1 on the hardware board. For more information on selecting CPUs for reference models, see Hardware Board Settings. The control algorithm, mPILBlock, is a separate model used by the reference model block. The mPILBlock reference model connects to the ADC Read (SoC Blockset) and PWM Write (SoC Blockset) blocks but does not contain any driver blocks itself.

Select the mPILBlock reference model. On the Model Block tab, set Simulation Mode to

Processor-in-the-loop (PIL).On the Apps tab, under Code Verification, Validation, and Test, click SIL/PIL Manager.

On the SIL/PIL tab, set System Under Test to

Model blocks in SIL/PIL mode. With the mPILBlock model block configured for PIL operation, code generated for only that reference model block alone and then deployed to the processor on the hardware board.Optionally, generate a PIL task profiling report. On the SIL/PIL tab, expand Settings and enable Task Profiling.

On the SIL/PIL tab, click Run SIL/PIL to run the simulation.

Top-Level PIL Simulation

In the top-level PIL simulation, code is generated for the top-level reference model and then deployed and executed on the connected hardware board. For detailed instructions on configuring a top-level PIL simulation, see Configure and Run PIL Simulation (Embedded Coder).

When using a top-level PIL simulation on C2000 Microcontroller Blockset models, the top-level reference model executes on the processor in the hardware board. However, due to the hybrid nature of the PIL setup, the model must meet these limitations.

All tasks must be timer-driven. Event-driven tasks are not supported.

Messages cannot be sent to the model block. As a result, driver blocks cannot be used in the models.

See Also

SIL and PIL Simulations (Embedded Coder) | PIL Simulation Sequence (Embedded Coder) | Hardware Board Settings | Configure and Run PIL Simulation (Embedded Coder)