Default System Reference Design for AMD SoC Device

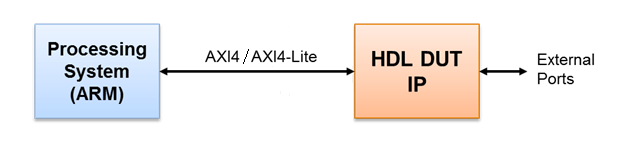

The HDL Coder™ software can generate an IP core with an AXI4 or an AXI4-Lite interface.

You can integrate the HDL IP core into the Default system

reference design.

The Default system is a basic reference design that

contains an ARM processor and the HDL IP core. HDL Coder generates the HDL DUT IP core, and

inserts it into the reference design. The processor acts as manager and the IP core acts

as subordinate. By accessing the generated registers via the AXI4-Lite interface, the

processor can read and write data to and from the IP core. You can tune the parameters

on the FPGA, or probe the results from the FPGA via the AXI4-Lite interface in the IP

core. To tune the parameters or probe results, use this reference design with

External mode in Simulink®.

To specify the Default system as the target reference

design:

Specify

IP Core Generationas target workflow. Open the HDL Workflow Advisor. In the Set Target Device and Synthesis Tool task, specifyIP Core Generationas the Target workflow.Specify

Default systemas target reference design. In the Set Target Reference Design task, for Reference design, selectDefault system.

Alternatively, you can also set the Default system

reference design from the Configuration Parameter dialog box.

In the Apps tab, click HDL Coder. In the HDL Code tab, in the Output section, set the drop-down button to IP Core.

Open the HDL Code Generation > Target tab of Configuration Parameters dialog box by clicking the Settings button.

Set the Workflow to

IP Core Generationand set the desired Target Platform from the supported boards listed in Board Support.Set the Reference Design parameter to

Default system.

To generate the HDL IP core, and integrate the IP core into the Default

system reference design, see Get Started with IP Core Generation from Simulink Model.

You can also specify whether the code generator inserts the AXI manager IP for the JTAG or programmable logic (PL) Ethernet connection and the data capture IP for the JTAG, PL Ethernet, processing system (PS) Ethernet, or universal serial bus (USB) Ethernet connection into the reference design. For more information about the available connections for AXI manager and FPGA data capture, see Set Target Reference Design.

For an example of automatic insertion of the AXI manager IP for the JTAG connection into a reference design, see Debug and Control Generated HDL IP Core by Using JTAG AXI Manager.

Board Support

You can use the Default system reference design

architecture with these target platforms:

Xilinx® Zynq® ZC702 evaluation kit

Xilinx Zynq ZC706 evaluation kit

ZedBoard™

Xilinx Versal® AI Core Series VCK190 Evaluation Kit.

Xilinx Zynq UltraScale+™ MPSoC ZCU102 evaluation kit