Resettable Subsystem Support in HDL Coder

This example shows how to use Resettable Subsystems in HDL Coder™.

Introduction to Resettable Subsystems

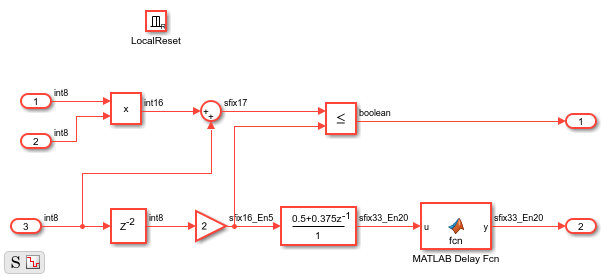

A Resettable Subsystem is a subsystem that will reset all states within the subsystem hierarchy based on a boolean control signal. It does this without requiring wiring the reset signal to each stateful block in Simulink®. This feature allows resetting blocks such as the MATLAB Function Block, which does not have an available reset port. For support in HDL Coder, a Resettable Subsystem is supported only within a Synchronous State Control region.

load_system('hdlcoder_resettable_subsystem'); open_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem'); set_param('hdlcoder_resettable_subsystem', 'SimulationCommand', 'update');

The Reset Block

A Resettable Subsystem looks similar to an Enabled Subsystem or any other Simulink conditionally executed subsystem in that it has a specialized Reset Port block inside it. This control port block has several trigger types available. HDL Coder supports the "level hold" trigger type.

open_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/LocalReset');

Resettable Subsystem Effects on Generated HDL code

Resettable Subsystems allow resetting the state of all blocks with state inside the subsystem to their initial value. In the generated HDL code, each design delay, a delay modeled explicitly in Simulink, has a reset added. Hardware implementation delays such as pipeline delays are not reset. The reset signal is a synchronous signal and is entirely independent from the global reset signal.

close_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/LocalReset'); makehdl('hdlcoder_resettable_subsystem/DUT'); type hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd

### Working on the model <a href="matlab:open_system('hdlcoder_resettable_subsystem')">hdlcoder_resettable_subsystem</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_resettable_subsystem/DUT')">hdlcoder_resettable_subsystem/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_resettable_subsystem', { 'HDL Code Generation' } )">hdlcoder_resettable_subsystem</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_resettable_subsystem'.

### Begin compilation of the model 'hdlcoder_resettable_subsystem'...

### Working on the model 'hdlcoder_resettable_subsystem'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_resettable_subsystem', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_resettable_subsystem'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_resettable_subsystem/gm_hdlcoder_resettable_subsystem.slx')">hdlsrc/hdlcoder_resettable_subsystem/gm_hdlcoder_resettable_subsystem.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_resettable_subsystem'.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/Discrete FIR Filter as hdlsrc/hdlcoder_resettable_subsystem/Discrete_FIR_Filter.vhd.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/MATLAB Delay Fcn as hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem as hdlsrc/hdlcoder_resettable_subsystem/Resettable_Subsystem.vhd.

### Working on hdlcoder_resettable_subsystem/DUT as hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_resettable_subsystem/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_resettable_subsystem' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem/DUT_report.html

### HDL check for 'hdlcoder_resettable_subsystem' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

-- -------------------------------------------------------------

--

-- File Name: hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd

-- Created: 2026-04-20 10:22:44

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

--

-- -------------------------------------------------------------

-- Rate and Clocking Details

-- -------------------------------------------------------------

-- Model base rate: 1

-- Target subsystem base rate: 1

--

--

-- Clock Enable Sample Time

-- -------------------------------------------------------------

-- ce_out 1

-- -------------------------------------------------------------

--

--

-- Output Signal Clock Enable Sample Time

-- -------------------------------------------------------------

-- Out1 ce_out 1

-- Out2 ce_out 1

-- -------------------------------------------------------------

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: DUT

-- Source Path: hdlcoder_resettable_subsystem/DUT

-- Hierarchy Level: 0

-- Model version: 20.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY DUT IS

PORT( clk : IN std_logic;

reset : IN std_logic;

clk_enable : IN std_logic;

LocalReset : IN std_logic;

In2 : IN std_logic_vector(7 DOWNTO 0); -- int8

In3 : IN std_logic_vector(7 DOWNTO 0); -- int8

In4 : IN std_logic_vector(7 DOWNTO 0); -- int8

ce_out : OUT std_logic;

Out1 : OUT std_logic;

Out2 : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END DUT;

ARCHITECTURE rtl OF DUT IS

-- Component Declarations

COMPONENT Resettable_Subsystem

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

In1 : IN std_logic_vector(7 DOWNTO 0); -- int8

In2 : IN std_logic_vector(7 DOWNTO 0); -- int8

In3 : IN std_logic_vector(7 DOWNTO 0); -- int8

LocalReset : IN std_logic;

Out1 : OUT std_logic;

Out2 : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : Resettable_Subsystem

USE ENTITY work.Resettable_Subsystem(rtl);

-- Signals

SIGNAL Resettable_Subsystem_Out1 : std_logic;

SIGNAL Resettable_Subsystem_Out2 : std_logic_vector(32 DOWNTO 0); -- ufix33

BEGIN

u_Resettable_Subsystem : Resettable_Subsystem

PORT MAP( clk => clk,

reset => reset,

enb => clk_enable,

In1 => In2, -- int8

In2 => In3, -- int8

In3 => In4, -- int8

LocalReset => LocalReset,

Out1 => Resettable_Subsystem_Out1,

Out2 => Resettable_Subsystem_Out2 -- sfix33_En20

);

Out1 <= Resettable_Subsystem_Out1;

Out2 <= Resettable_Subsystem_Out2;

ce_out <= clk_enable;

END rtl;

The MATLAB Function Block does not have support for an explicit reset port. When placed in a Resettable Subsystem, HDL Coder will generate a synchronous external reset signal to control the resetting of persistent variables inside the function.

function y = fcn(u)

persistent state;

if isempty(state)

state = fi(0, 1, 33, 20);

endy = state; state = u; end

type hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd

-- -------------------------------------------------------------

--

-- File Name: hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd

-- Created: 2026-04-20 10:22:44

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: MATLAB_Delay_Fcn

-- Source Path: hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/MATLAB Delay Fcn

-- Hierarchy Level: 2

-- Model version: 20.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY MATLAB_Delay_Fcn IS

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

u : IN std_logic_vector(32 DOWNTO 0); -- sfix33_En20

LocalReset : IN std_logic;

y : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END MATLAB_Delay_Fcn;

ARCHITECTURE rtl OF MATLAB_Delay_Fcn IS

-- Signals

SIGNAL u_signed : signed(32 DOWNTO 0); -- sfix33_En20

SIGNAL y_tmp : signed(32 DOWNTO 0); -- sfix33_En20

BEGIN

u_signed <= signed(u);

MATLAB_Delay_Fcn_1_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

y_tmp <= to_signed(0, 33);

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

IF LocalReset = '1' THEN

y_tmp <= to_signed(0, 33);

ELSE

y_tmp <= u_signed;

END IF;

END IF;

END IF;

END PROCESS MATLAB_Delay_Fcn_1_process;

y <= std_logic_vector(y_tmp);

END rtl;

A synchronous delay signal named LocalDelay has been added to the VHDL code generated for the delay implemented in the MATLAB Function block.