Multiply-Accumulate

Perform a multiply-accumulate operation on the inputs

Libraries:

HDL Coder /

HDL Operations

Description

The Multiply-Accumulate block performs this operation on inputs

a , b, and bias c to

compute result dataOut.

dataOut = sum(a.* b) + c

By default, the block operates in the vector mode. The inputs a and

b can be scalars, vectors, or 2-D matrices. By default, the bias

value c is equal to zero. The block computes the dot product of

inputs a and b. You can specify a nonzero value

for c by using Dialog or Input

port as the Source. The block adds this bias to the

dot product of a and b. The multiplication

operation is full precision irrespective of the Output data type

setting. The Output data type and Integer rounding

mode settings apply to the addition operation. To generate HDL code for

the block, use vector inputs. For scalar inputs, use the Multiply-Add block.

By using the Operation Mode setting, you can specify streaming

modes of operation for the Multiply-Accumulate block. For HDL code

generation, when you use the streaming operation mode, you must input scalar values to

the block. The block has two streaming modes: Streaming - using Start and End

ports and Streaming - using Number of Samples. When you

select these streaming modes, you can specify the control signals to use with the mode.

The control signals specify when to start and end accumulation and when the output is

valid.

Ports

Input

Port to provide input to the block.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port to provide input to the block.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point | enumerated | bus

Port to provide the bias signal to the block. The block adds this bias to the inputs. Make sure that the bias signal data type matches that of the dot product of the inputs.

Dependencies

To enable this port, set Source to

Input port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port to provide the control signal to start accumulation. It is

recommended that you use a boolean data type signal

as input to the port. To start obtaining the accumulated output value

from the dataOut signal, both

startIn and validIn

signals must be high. The dataOut signal produces

the accumulated result from the next clock cycle.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End

Ports.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port to provide the control signal to indicate that the input signal

is valid for accumulation. It is recommended that you use a

boolean data type signal as input to the port. To

start obtaining the accumulated output value from the

dataOut signal, both

validIn and startIn

signals must be high. The dataOut signal produces

the accumulated result from the next clock cycle. The

validIn signal has higher priority than

startIn and endIn

signals.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End Ports

or Streaming - using Number of Samples.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port to provide the control signal to indicate end of accumulation. You can use the startIn and endIn signals with the validIn signal to indicate a frame that contains the accumulated output.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End Ports

and then select End input and output ports.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Output

Port that generates the output data from the multiply-accumulate

operation. By default, the block uses the

Vector mode of operation and computes the

dot product of the input signals, and adds the bias to produce the

result. If you specify a streaming mode of operation as

Operation Mode, the value of the

dataOut signal depends on the control signals

that you provide. The data type of the output signal is same as that of

the accumulator.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port that generates output control signal to indicate the start of accumulation. When both validIn and startIn are high, the startOut signal becomes high in the next clock cycle. The clock cycle at which startOut becomes high indicates the start of a frame and that the dataOut signal has started producing valid accumulated output.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End Ports

and then select Start output port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port that generates the output control signal to indicate that the dataOut signal is valid. When the validIn signal becomes high , the validOut signal becomes high in the next clock cycle and indicates that the dataOut is valid.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End Ports

and then select Valid output port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port that generates the output control signal to indicate the end of accumulation. You can use the clock cycles between when the startOut signal becomes high and when the endOut signal becomes high to indicate a valid frame that contains the accumulated output.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End Ports

and then select End input and output ports.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Port that generates the output control signal to indicate number of

samples to accumulate. The value of this signal increases from

1 to the value that you specify for

Number of Samples. As long as the

validIn signal is high, the

countOut increments by 1

every clock cycle.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Number of Samples

and then select Count output port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

Parameters

You can specify the Operation Mode as:

Vector: You can use scalars or vectors as inputs. The block performs the dot product of the inputsu1andu2and adds biaskto produce the result.Streaming - using Start and End Ports: Use scalar inputs for HDL code generation. In this mode, you can use the startIn and endIn control signals to determine when to start and stop accumulation. The output data is valid when validIn is high.Streaming - using Number of Samples: Use scalar inputs for HDL code generation. In this mode, you can specify the Number of Samples and use the countIn control signal to determine when to start and stop accumulation. The output data is valid when validIn is high.

Programmatic Use

Block parameter:

opMode |

| Type: character vector |

Value:

'Vector' | 'Streaming - using Start and

End Ports' | 'Streaming - using Number of

Samples' |

Default:

'Vector' |

You can specify the bias with:

Source as

Dialog. Then, specify the Value.Source as

Input port. This setting creates an external input portcto input the bias signal to the block.

Programmatic Use

Block parameter:

initValueSetting |

| Type: character vector |

Value:

'Dialog' | 'Input

port' |

Default:

'Dialog' |

If you set Source as Dialog,

you can specify the initial value by using the

initValue2 setting.

Block parameter:

initValue2 |

| Type: character vector |

| Value: An integer greater than or equal to zero |

Default:

'0.0' |

You can specify the Number of Samples to specify a frame containing the number of samples of valid accumulated output dataOut.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Number of

Samples.

Programmatic Use

Block parameter:

num_samples |

| Type: character vector |

| Value: An integer greater than or equal to zero |

Default:

'2' |

Set the output data type to:

A rule that inherits a data type, such as

Inherit: Same as first input.A built-in data type, such as

singleorint16.The name of a data type object. for instance, a

Simulink.NumericTypeobject.An expression that evaluates to a valid data type, for example,

fixdt(1,16,0)

The streaming modes do not support Inherit: Inherit via internal

rule. When you set the Output data type,

you can use the Data Type Assistant. To display the

assistant, click the Show data type assistant

![]() .

.

Programmatic Use

Block parameter:

OutDataTypeStr |

| Type: character vector |

Default:

{'Inherit: Inherit via internal rule'} |

To see possible values that you can specify for this parameter, see Programmatically Specify Block Parameters and Properties.

Specify the rounding action as:

CeilingRounds positive and negative numbers toward positive infinity. Equivalent to the MATLAB®

ceilfunction.ConvergentRounds number to the nearest representable value. If a tie occurs, rounds to the nearest even integer. Equivalent to the Fixed-Point Designer™

convergentfunction.FloorRounds positive and negative numbers toward negative infinity. Equivalent to the MATLAB

floorfunction.NearestRounds the number to the nearest representable value. If a tie occurs, rounds toward positive infinity. Equivalent to the Fixed-Point Designer

nearestfunction.RoundRounds number to the nearest representable value. If a tie occurs, rounds positive numbers toward positive infinity and rounds negative numbers toward negative infinity. Equivalent to the Fixed-Point Designer

roundfunction.SimplestChooses between rounding toward floor and rounding toward zero to generate rounding code that is as efficient as possible.

ZeroRounds number toward zero. Equivalent to the MATLAB

fixfunction.

Programmatic Use

Block parameter:

RndMeth |

| Type: character vector |

Default:

{'Floor'} |

To see possible values that you can specify for this parameter, see Programmatically Specify Block Parameters and Properties.

Control generation of the validOut output port. This port indicates whether dataOut is valid.

off

offDoes not display the validOut output port.

on

onDisplay the validOut output port.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Number of Samples or

Streaming - using Start and End

Ports.

Programmatic Use

Block parameter:

validOut |

| Type: character vector |

Values:

'off' | 'on' |

Default:

'off' |

Control generation of the endIn input port and the endOut output port. The ports indicate the end of a frame containing valid accumulation output.

off

offDoes not display the endIn input port and the endOut output port.

on

onDisplay the endIn input port and the endOut output port.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End

Ports.

Programmatic Use

Block parameter:

endInandOut |

| Type: character vector |

Values:

'off' | 'on' |

Default:

'off' |

Control generation of the startOut output port. This port generates the startOut signal that indicates the start of a frame containing valid accumulated output.

off

offDoes not display the startOut output port.

on

onDisplay the startOut output port.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Start and End

Ports.

Programmatic Use

Block parameter:

startOut |

| Type: character vector |

Values:

'off' | 'on' |

Default:

'off' |

Control generation of the countOut output port. This port generates the counter that indicates a frame containing valid samples.

off

offDoes not display the countOut output port.

on

onDisplay the countOut output port.

Dependencies

To enable this port, set Operation Mode to

Streaming - using Number of

Samples.

Programmatic Use

Block parameter:

countOut |

| Type: character vector |

Values:

'off' | 'on' |

Default:

'off' |

Tips

With the Multiply-Accumulate block, you can:

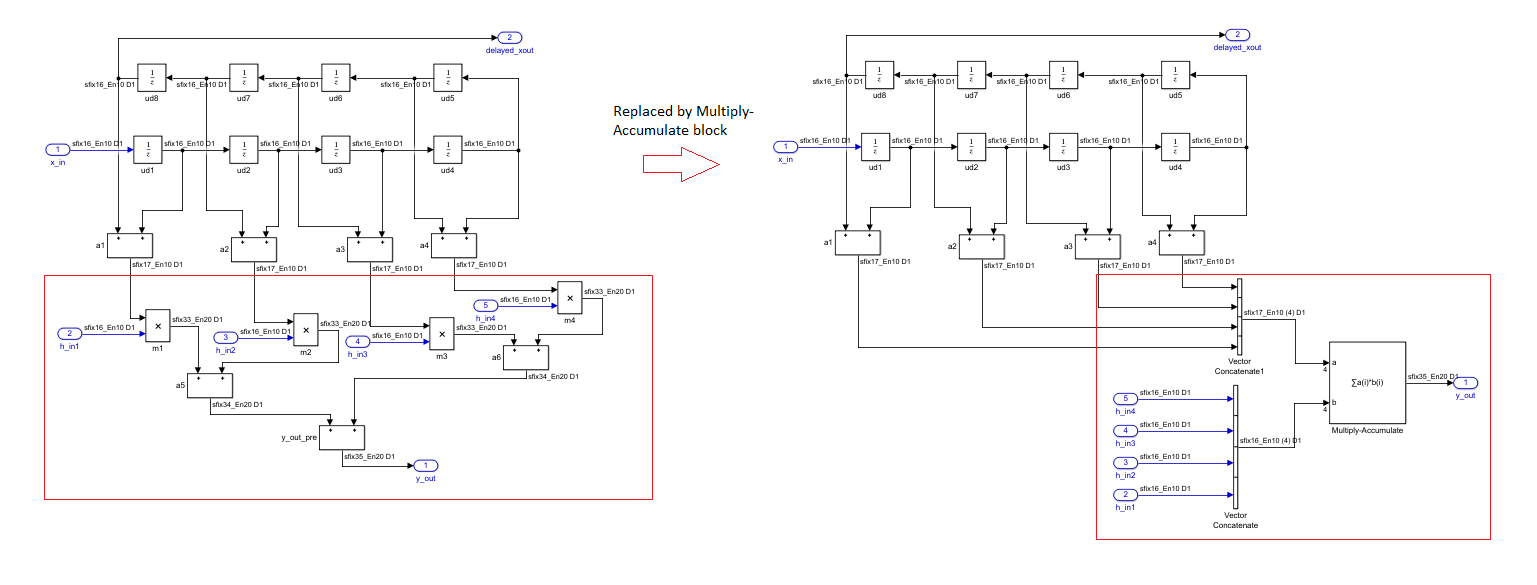

Perform matrix multiplication operations. For example, if you have two matrix inputs with dimensions

N-by-MandM-by-P, you can compute the result by usingN-by-Pmultiply-accumulate operations in parallel.Replace a sequence of multiplication and addition operations, such as in filter blocks, and improve the performance on hardware by mapping to DSP slices on the FPGA. This figure shows how you can use the Multiply-Accumulate block with the

sfir_fixedmodel.

Algorithms

You can use the Operation Mode setting for the block to

specify a streaming mode of operation. When you select Streaming - using

Start and End Ports, you see three additional settings enabled by

default. The settings include:

Valid output port

End input and output ports

Start output port

It is recommended that you leave these settings enabled. When you apply the settings, three additional input ports and three additional output ports appear:

| Input Ports | Output Ports |

|---|---|

| startIn | startOut |

| validIn | validOut |

| endIn | endOut |

This figure illustrates the streaming mode of operation using the start and end

ports. In this example, the bias value is 8.

Initially, when validIn is low, dataOut

is zero. At time 1s, both startIn and

validIn become high. Therefore,

validOut becomes high in the next clock cycle and

dataOut starts producing valid accumulation output. During

accumulation, dataOut takes the values of

a and b from the previous clock cycle.

For example, at time t = 2s, dataOut = 1*1 +

8 = 9.

To continue accumulation, make startIn low at the next clock cycle and keep validIn high. dataOut continues accumulating the inputs until validIn becomes low. At each time step, dataOut computes the product of the inputs from the previous clock cycle and sums the result with the dataOut value from the previous clock cycle. For example, at time t = 3s, dataOut = 2*2 + 9 = 13.

When validIn becomes low, dataOut holds the output value as seen at time t = 5s. At t = 5s, endIn and validIn are high. Therefore, endOut becomes high in the next clock cycle, which indicates end of frame. Therefore the frame between t = 2s (when startOut is high) and t = 6s (when endOut is high) indicates a frame containing valid output.

If startIn, validIn, and endIn are both high at the same time, only the dataOut corresponding to those inputs are accumulated as seen at t = 8s. If startIn is high for multiple clock cycles, and if validIn is high, the accumulator is reset at each clock cycle as seen at t = 10s and t = 11s. The accumulation continues at t = 12s.

You can use the Operation Mode setting for the block to

specify a streaming mode of operation. When you select Streaming - using

Number of Samples, you see two additional settings enabled by default.

The settings include:

Valid output port

Count output port

It is recommended that you leave these settings enabled. When you apply the settings, you have an additional input port validIn and three additional output ports appear:

endOut

validOut

countOut

This figure illustrates the streaming mode of operation using the number of

samples. In this example, the bias value is 8 and the

Number of Samples is 5.

Initially, when validIn is low, dataOut

is 0 and countOut is 1.

At time 1s, validIn becomes high. Therefore,

validOut becomes high in the next clock cycle, and

dataOut starts producing valid accumulation output. During

accumulation, dataOut takes the values of

a and b from the previous clock cycle.

For example, at time t = 2s, dataOut = 1*1 =

1. countOut increments by

1 at the next clock cycle, that is, at t =

3s, countOut becomes

2.

To continue accumulation, keep validIn high.

dataOut continues accumulating the inputs until

validIn becomes low. When five valid outputs are obtained

from dataOut, countOut becomes

5 and endOut becomes high, which

indicates the end of the frame. Therefore, the time between when

countOut is 1 and when

countOut is five indicates a frame containing valid

output.

The accumulator counter is now reset and countOut starts from

1. When validIn becomes high again,

dataOut starts accumulating a new set of values and

countOut starts incrementing for each valid

dataOut.

Extended Capabilities

C/C++ Code Generation

Generate C and C++ code using Simulink® Coder™.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

| HDL Architecture Setting | Description |

|---|---|

Parallel | For input vectors of size |

Serial(Default) | For input vectors of size

When you synthesize your design, depending on the input bit widths, this architecture maps to one DSP slice on the FPGA. |

| General | |

|---|---|

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes. |

When you use complex signals, this block can generate HDL code, but does not map to DSP slices.

For the mapping of the Multiply-Accumulate block to DSP slices, use these reset type settings:

For Xilinx® FPGA boards, set Reset type to

Synchronous.For Altera® FPGA boards, set Reset type to

Asynchronous.

To set the reset type, select HDL Code Generation > Global settings > Clock settings > Reset type.

Matrix data types are not supported at the block port interfaces. If you have matrix type signals, use the Product, Matrix Multiply block in matrix multiplication mode.

Streaming modes of operation for the block are not supported inside a Resettable Subsystem block for HDL code generation.

The block does not support floating-point data types for HDL code generation.

Version History

Introduced in R2017bUse the SynthesisAttributes HDL block property to specify the synthesis attributes for the block and its output signals. HDL Coder includes these attributes in the generated HDL code.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)