TH Rosenheim Uses HDL Coder to Develop ASICs for High-Precision Control Drives

Using Model-Based Design, Researchers Developed an ASIC in Nine Months

“Simulink and HDL Coder enabled us to fabricate our ASIC in just nine months, a process that would have taken twice as long with our limited HDL and ASIC expertise. An ASIC workflow in HDL Coder allowed us to quickly generate HDL and iterate through the ASIC toolchain, achieving our power, performance, and area goals. Our latest chip from X-FAB was 100% silicon-proven, thanks in part to HDL Verifier.”

Key Outcomes

- Successfully designed, implemented, and verified a high-performance ASIC for servo drive control

- Achieved higher switching frequency and enhanced control loop dynamics within a 120 mW power budget, which is 33x lower than the corresponding FPGA prototype

- Streamlined the workflow from model to ASIC, reducing development time by several months

- Delivered an error-free ASIC with verified control loops up to 200 KHz and ±1.6 nm position stability

Research engineers at Germany’s Technical University of Applied Sciences (TH Rosenheim) needed a configurable servo drive controller for high-acceleration, high-accuracy control at their voice coil motor test stand. Such high-precision drives are essential in the semiconductor industry for precise positioning. Traditional software-based controller implementations could not handle the PWM frequencies of 200 kHz and above required in such applications. TH Rosenheim therefore decided to design a custom ASIC to achieve higher switching frequency with a power budget of 120 mW. The increased switching frequency achieved through wide-bandgap semiconductors enables significantly enhanced control loop dynamics. Additionally, TH Rosenheim wanted to adapt the model developed for FPGA prototyping to create the ASIC with minimal modifications.

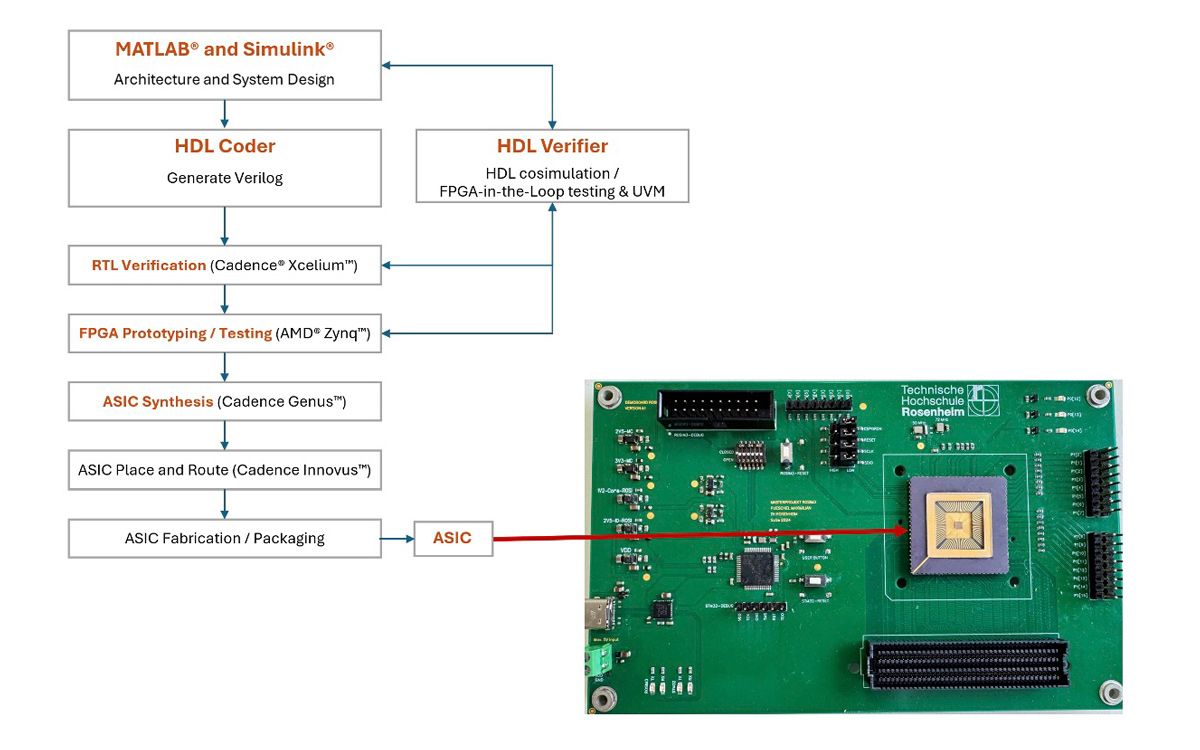

With limited experience in HDL programming and ASIC design, TH Rosenheim engineers used a MATLAB® and Simulink® to ASIC workflow provided by HDL Workflow Advisor in HDL Coder™. They designed the controller and its SPI communication interface in Simulink and verified it via simulation. They generated Verilog® using HDL Coder and deployed it to an FPGA for prototyping. The team used HDL Verifier™ features for cosimulation and FPGA-in-the-loop testing to verify the correct implementation of the Simulink model in HDL—and in hardware—allowing them to iteratively identify and fix design issues. Additionally, they generated UVM testbenches for their ASIC verification workflow.

Thanks to outstanding collaboration with the MathWorks development team, the Cadence® Genus™ ASIC synthesis tool is now supported in HDL Workflow Advisor. The team synthesized the generated HDL with a minimum number of settings. The genhdltdb feature provided precise timing estimates during the modeling phase using the Cadence Genus tool and ASIC technology node data. This significantly reduced iteration loops for identifying timing issues and shortened this step from six weeks to just a few days.

The complete process from model creation to ASIC fabrication took just nine months instead of over a year, with 99% of the final production ASIC-grade HDL generated by HDL Coder. Testing confirmed the ASIC to be completely error-free, with control loop verifications up to 200 kHz and a position stability of ±1.6 nm.

TH Rosenheim developed its ASIC using Model-Based Design and HDL Coder, manufactured by X-FAB with a 180 nm technology node. This year, TH Rosenheim plans to develop an ASIC using a 28 nm HPC+ node from TSMC.